Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

Tags

- Automotive

- Barium titanate

- X7T

- bme

- coating

- CERAMIC

- halt

- core-shell

- dispersion

- CSZT

- nickel

- Powder

- Zirconia

- hydrothermal

- EV

- NI-MLCC

- Sintering

- reliability

- paste

- X8R

- C0G

- BaTiO3

- ZrO2

- oxygen vacancy

- ASSB

- mlcc

- nano powder

- Murata

- microstructure

- ni-paste

Archives

- Today

- Total

MLCC Material & Process

(2020) Low-ESL MLCCs by SEMCO 본문

https://www.roger-tech.com/kr/news/Samsung-Electro-Mechanics-Technical-Document-Low-ESL-MLCC.html

Just a moment...

Just a moment... We're checking your browser before accessing our website.

www.roger-tech.com

인터넷에서 찾은 삼성전기의 Low-ESL MLCC관련자료를 Notebook LM의 도움으로 설명을 보완하여 공유드립니다

-------------------------------------------------------------------------------------------------------------------------------------------------

1장. Why Low-ESL MLCC? (왜 Low-ESL MLCC인가?) : 실제 MLCC의 특성과 낮은 ESL의 필요성 및 시스템 트렌드에 대해 설명합니다.

실제 MLCC의 특성 및 낮은 ESL의 효과

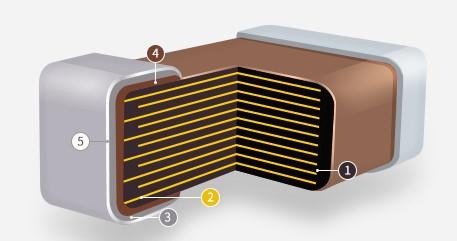

• 실제 MLCC의 구성: 실제 MLCC(Multilayer Ceramic Capacitor)는 이상적인 커패시터와 달리 커패시턴스(C), 등가 직렬 저항(ESR: Equivalent Series Resistance), 등가 직렬 인덕턴스(ESL: Equivalent Series Inductance)를 모두 가집니다.

• 임피던스 (Z) 공식: 실제 MLCC의 임피던스는 로 표현됩니다.

• ESR 및 ESL의 원인:

◦ ESR은 유전체 저항(Dielectric Resistance) 및 내부/외부 저항(Internal/External Resistance)으로 인해 발생합니다.

◦ ESL은 전류 변화(Current Variance)와 자속 변화(Flux Variance)가 기전력(EMF: Electromotive Force)을 생성하여 발생합니다.

• 전압 변동 감소 효과: 커패시터의 낮은 ESL은 전압 변동(voltage fluctuations, \Delta V)을 감소시킬 수 있습니다. 벅 컨버터(Buck Converter) 회로에서 ESL 값이 감소할수록 (예: 500 pH에서 100 pH로) 출력 전압의 변동 폭 ()이 현저히 줄어드는 것을 시뮬레이션을 통해 보여줍니다.

• 임피던스(Z) 관계: 전압 변동()은 임피던스()에 비례합니다 ().

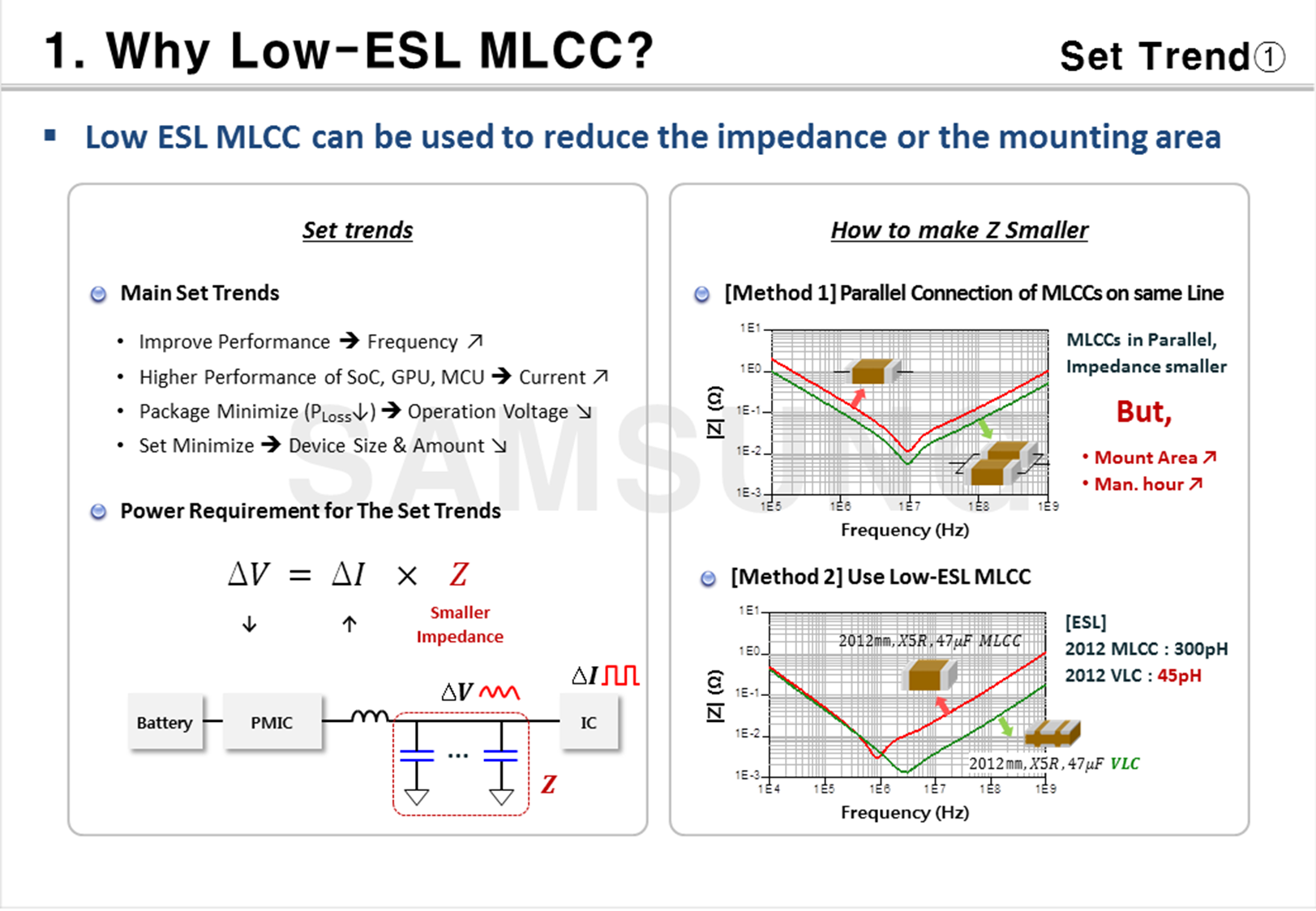

세트 트렌드와 Low-ESL MLCC의 활용

• 주요 세트 트렌드: 성능 향상 주파수() 증가; SoC/GPU/MCU의 고성능화 전류() 증가; 패키지 최소화() 동작 전압() 감소; 세트 최소화 디바이스 크기 및 수량() 감소 추세입니다.

• 전력 요구사항: 관계에서, 를 줄이기 위해 임피던스()를 작게 만들어야 합니다.

• Z를 줄이는 방법:

1. 방법 1: MLCC를 같은 라인에 병렬 연결: 임피던스는 감소시키지만, 마운트 면적(Mount Area)이 증가하고 작업 시간(Man. hour)이 늘어납니다.

2. 방법 2: Low-ESL MLCC 사용: 예를 들어, 2012mm MLCC (300 pH) 대신 Low-ESL MLCC인 2012 VLC (45 pH)를 사용하여 임피던스를 줄일 수 있습니다.

• 스마트폰 PDN 트렌드: AP/SoC/GPU의 성능 향상에 따라 3단자 커패시터(3T Cap)와 로우 프로파일 커패시터의 사용이 증가하고 있습니다.

◦ 공간 절약 트렌드: 저성능(Phase 1) 단계에서는 많은 수의 22uF MLCC를 사용했지만, 고성능(Phase 3) 단계에서는 고용량 3T 커패시터(3T 15uF)와 LSC(Low Self-Inductance Capacitor) 또는 임베디드 커패시터 등을 사용하여 고주파수 디커플링에서 ESL을 낮추며 공간을 절약합니다.

• PDN 내 커패시터의 기능 범위:

◦ MLCC: 수백 kHz 대역.

◦ 3단자(3T): 수백 kHz에서 수십 MHz 대역.

◦ LSC: 수십 MHz 이상 대역에서 임피던스 감소를 담당합니다.

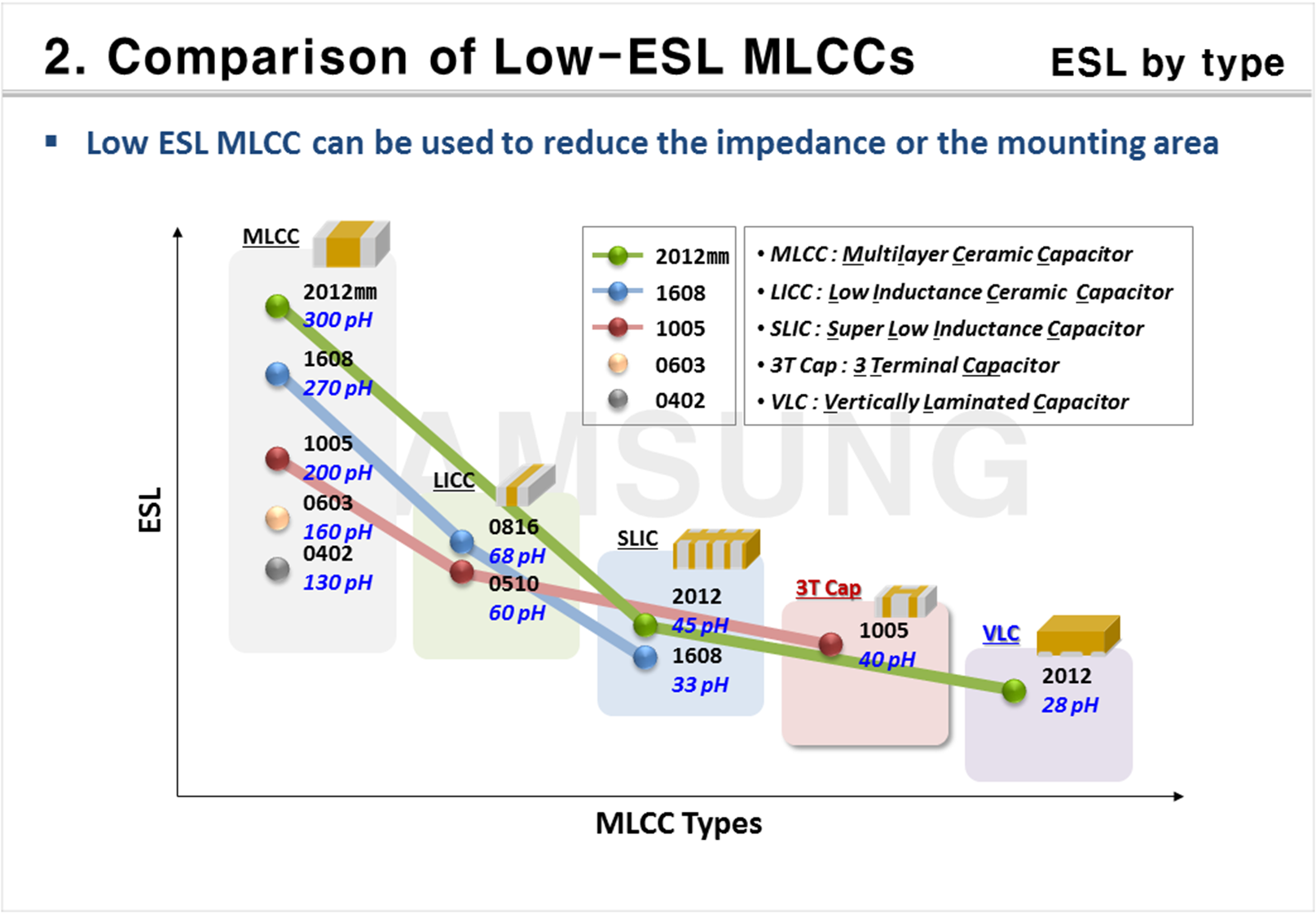

2장. Comparison of Low-ESL MLCCs (Low-ESL MLCC 비교) : 다양한 Low-ESL MLCC 유형의 ESL 성능 및 구조적 원리를 비교합니다.

ESL 유형별 비교

Low ESL MLCC는 임피던스 또는 마운팅 면적을 줄이는 데 사용될 수 있습니다.

|

유형 (약어)

|

전체 명칭

|

예시 ESL 값 (2012mm 기준)

|

|

MLCC

|

Multilayer Ceramic Capacitor

|

300 pH (2012mm), 130 pH (0402)

|

|

LICC

|

Low Inductance Ceramic Capacitor

|

60 pH (0816), 130 pH (0402)

|

|

SLIC

|

Super Low Inductance Capacitor

|

45 pH (2012), 33 pH (1608)

|

|

3T Cap

|

3 Terminal Capacitor

|

40 pH (1005)

|

|

VLC

|

Vertically Laminated Capacitor

|

28 pH (2012)

|

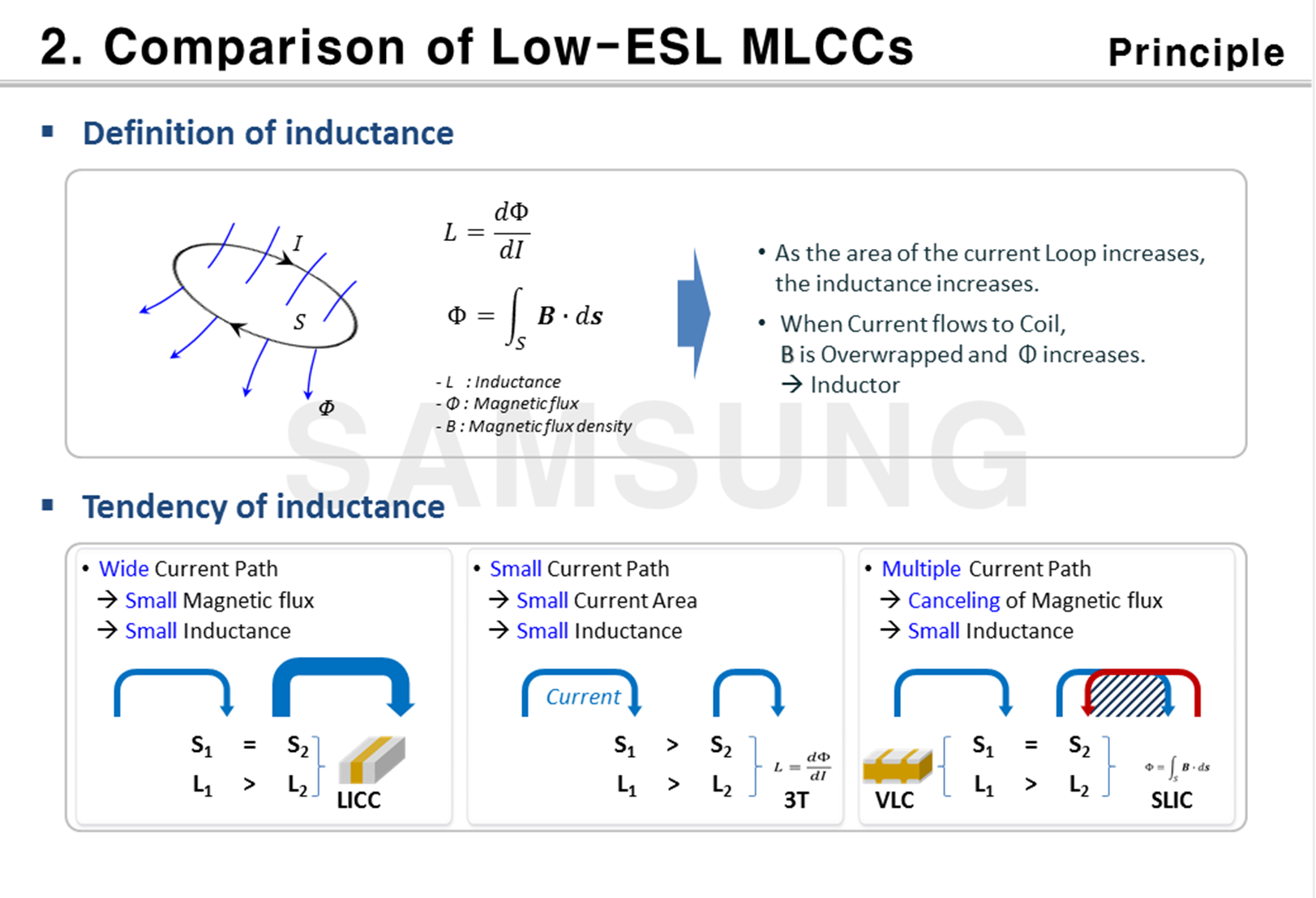

인덕턴스의 원리 및 경향

• 인덕턴스의 정의: (: 자기장, : 전류)이며, 전류 루프의 면적이 증가하면 인덕턴스가 증가합니다.

• Low Inductance를 달성하는 구조적 경향:

◦ Wide Current Path (LICC): 자기장()을 작게 만들어 인덕턴스를 작게 만듭니다.

◦ Small Current Path (3T): 전류 면적()을 작게 만들어 인덕턴스를 작게 만듭니다.

◦ Multiple Current Path (VLC, SLIC): 자기장 소거(Canceling of Magnetic flux)를 통해 인덕턴스를 작게 만듭니다.

Low-ESL MLCC 유형별 구조

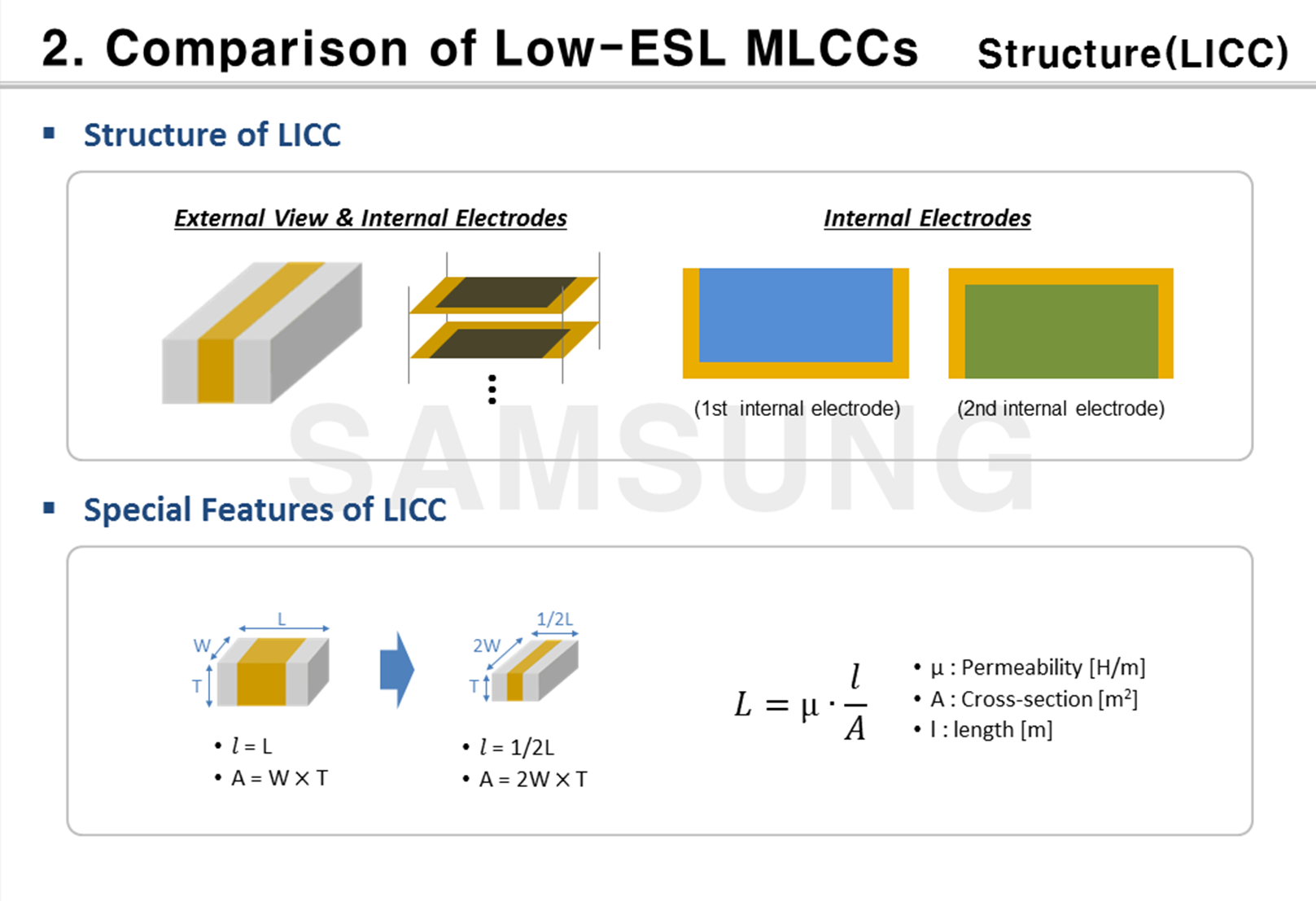

• LICC (Low Inductance Ceramic Capacitor):

◦ 특징: 인덕턴스 공식을 바탕으로, 길이()를 줄이고 단면적()을 늘리는 구조적 특징을 가집니다. 일반 MLCC 대비 이 로 줄고 가 로 늘어납니다.

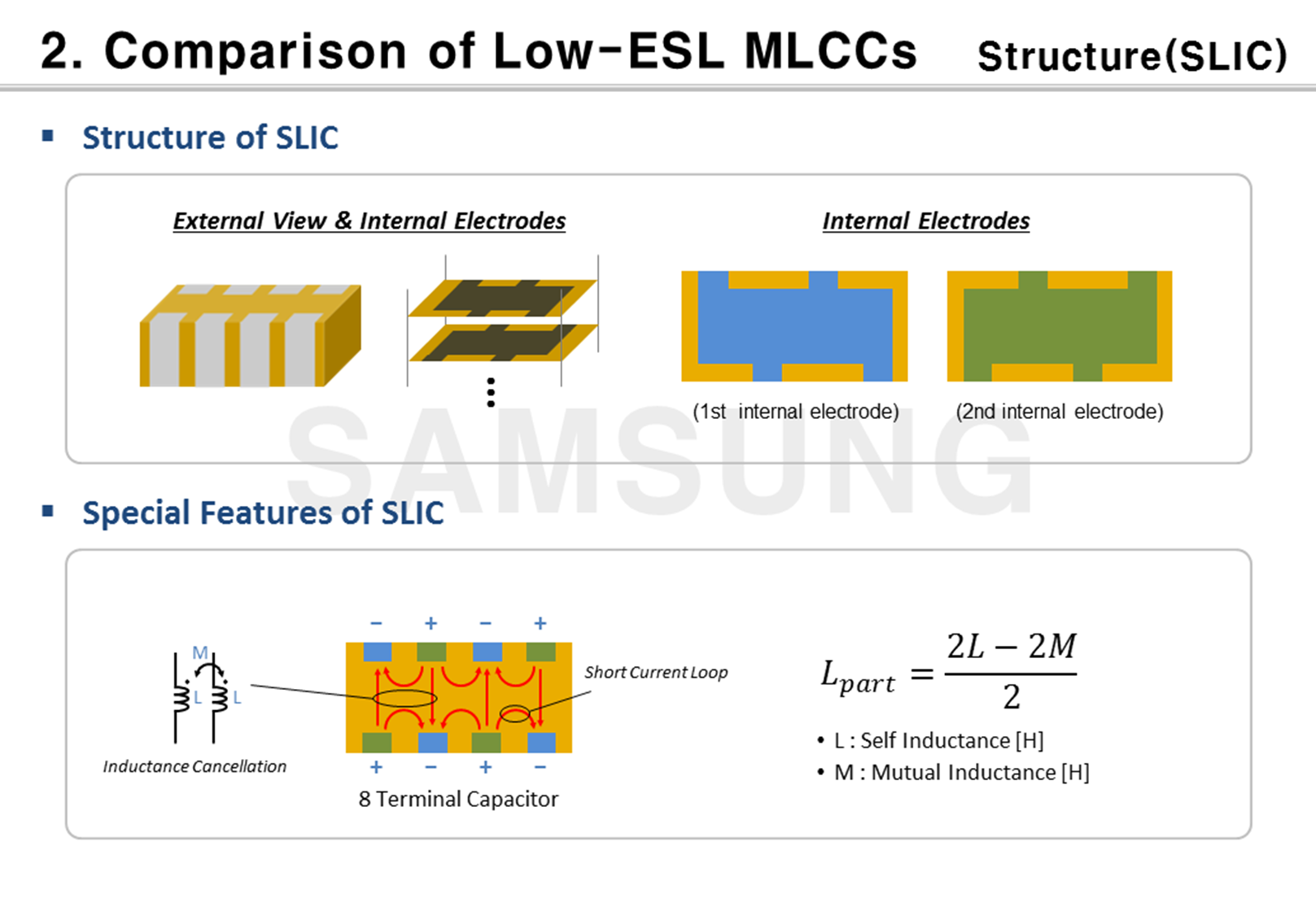

• SLIC (Super Low Inductance Capacitor):

◦ 특징: **인덕턴스 상쇄(Inductance Cancellation)**를 이용하며, 8단자 커패시터 형태를 가집니다. 짧은 전류 루프(Short Current Loop)를 형성하여 를 통해 인덕턴스를 낮춥니다 (: 자기 인덕턴스, : 상호 인덕턴스).

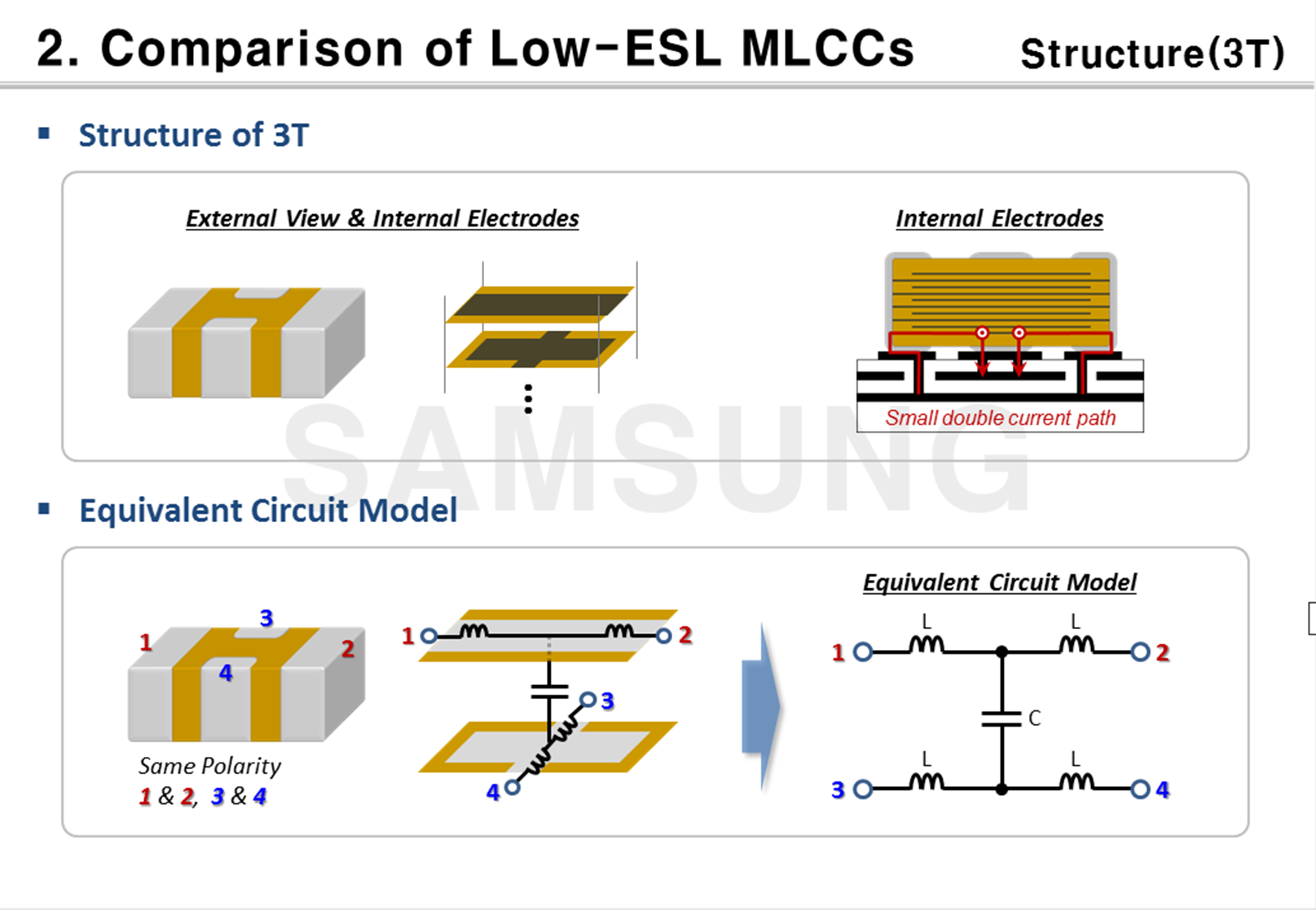

• 3T (3 Terminal Capacitor):

◦ 특징: **작은 이중 전류 경로(Small double current path)**를 형성합니다. 등가 회로 모델은 커패시턴스(C)가 두 개의 분리된 인덕턴스 경로(L) 사이에 연결된 형태입니다.

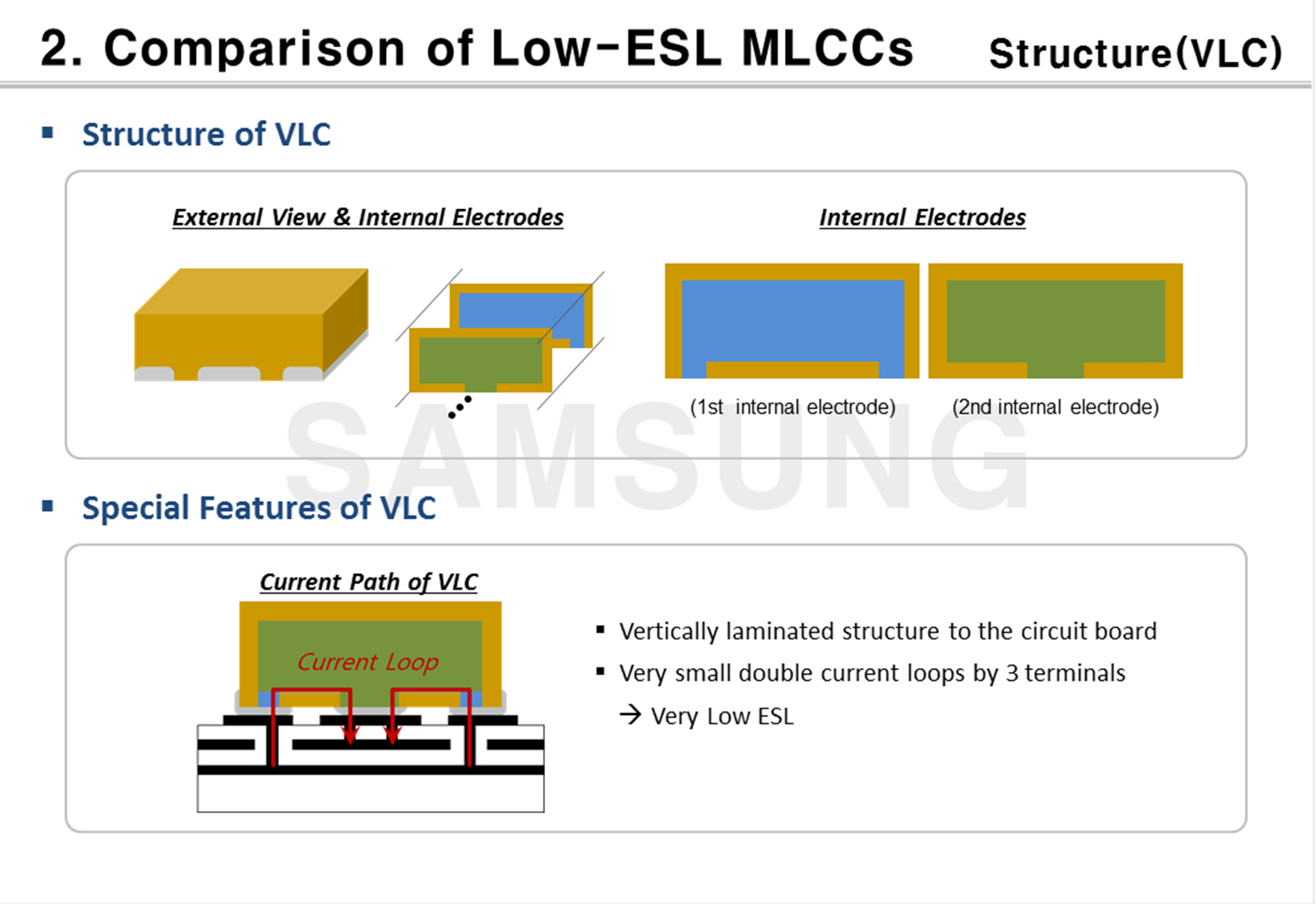

• VLC (Vertically Laminated Capacitor):

◦ 특징: 회로 기판에 수직으로 적층된 구조(Vertically laminated structure)를 가집니다. 3개의 단자를 통해 매우 작은 이중 전류 루프를 형성하여 **매우 낮은 ESL(Very Low ESL)**을 달성합니다.

3장. Performance (성능) : Low-ESL MLCC, 특히 3단자 커패시터(3T Cap)의 임피던스, 공간 활용 및 전압 리플 성능을 평가합니다.

유형별 임피던스 (Z) 비교

• 3단자 커패시터는 MLCC 및 LICC보다 낮은 ESL을 보여줍니다. 삽입 손실(Insertion Loss, S21) 그래프를 통해 커패시턴스 영역과 ESL 영역을 비교할 때, 3T Cap이 가장 낮은 ESL 성능을 보입니다.

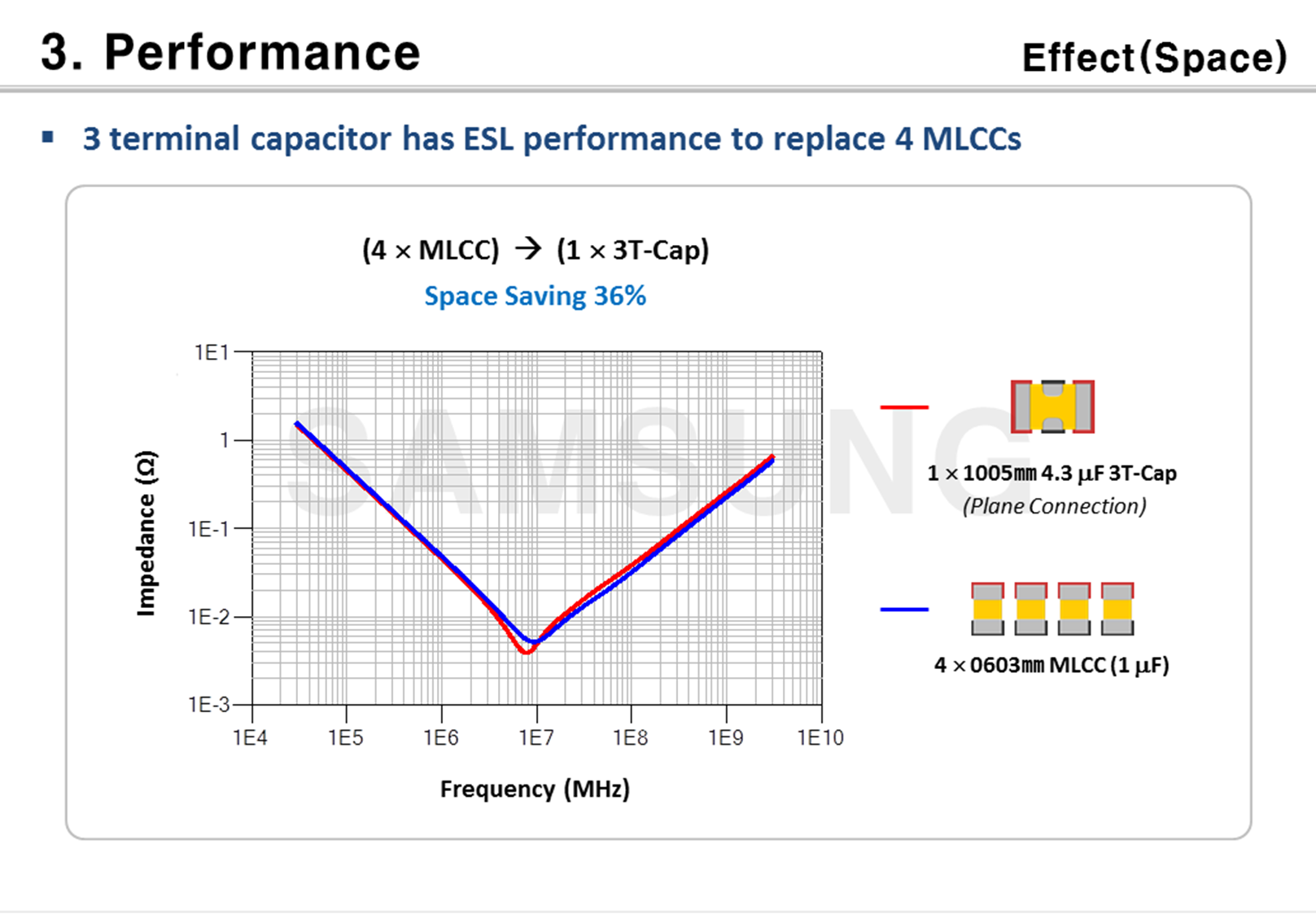

공간 효율 (Space Effect)

• 3단자 커패시터는 4개의 MLCC를 대체할 수 있는 ESL 성능을 가집니다.

• MLCC (1 씩)를 3T Cap (4.3 )으로 대체할 경우, 유사한 임피던스 곡선을 유지하면서 36%의 공간 절약(Space Saving 36%) 효과를 얻을 수 있습니다.

전압 리플 효과 ( Effect)

• 3T Cap은 MLCC보다 더 작은 전압 리플(\Delta V)을 보입니다.

◦ 과도 시뮬레이션(Transient Simulation) 결과 비교 (PMIC 3Vdc, I=3A, T=15ns):

▪ MLCC 사용 시: .

▪ 3T Cap 사용 시: \Delta V = 162 mV.

• 디자인 인(Design-In) 성능 비교:

◦ MLCC (HHP 설계 기준) 사용 시: .

◦ 3T Cap 사용 시: .

◦ 이 비교를 통해, 1개의 3T Cap이 4개의 MLCC가 달성한 것과 거의 동일한 리플 성능을 제공함을 알 수 있습니다.

NotebokLM의 도움으로 제작되었습니다

'Product' 카테고리의 다른 글

| (2018) Murata Capacitor for Jacinto 7 (0) | 2025.10.26 |

|---|---|

| (2012) Murata Technology for commodification of small size MLCC with high capacitance for Space Application (0) | 2023.05.29 |

| (2015) Murata MLCC promotion (0) | 2023.05.29 |

| (2020) 전장용 MLCC 기술전망 (삼성전기 정해석 개발팀장) (0) | 2023.05.29 |

| (2021)TDK의 테크놀로지 Vol 4. MLCC와 미세구조 제어 (0) | 2023.05.28 |