Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

Tags

- BaTiO3

- coating

- ni-paste

- microstructure

- X8R

- oxygen vacancy

- CSZT

- reliability

- hydrothermal

- C0G

- X7T

- Sintering

- NI-MLCC

- EV

- Barium titanate

- halt

- core-shell

- Zirconia

- ZrO2

- nickel

- CERAMIC

- Murata

- dispersion

- Automotive

- bme

- mlcc

- Powder

- paste

- nano powder

- ASSB

Archives

- Today

- Total

MLCC Material & Process

(2018) Murata Capacitor for Jacinto 7 본문

Texas Instruments (TI)의 Jacinto 7 프로젝트를 위해 Low ESL 커패시터를 활용한 전력 설계 최적화 방안을 제안하는 자료가 인터넷에 있어 이를 정리해 봅니다

이 제안은 주로 Jacinto 6+ 보드에 대한 분석 및 시뮬레이션 결과를 기반으로, 부품 수 감소(Cost down), 소형화(Downsizing), 그리고 저 임피던스(Low impedance) 실현을 목표로 합니다

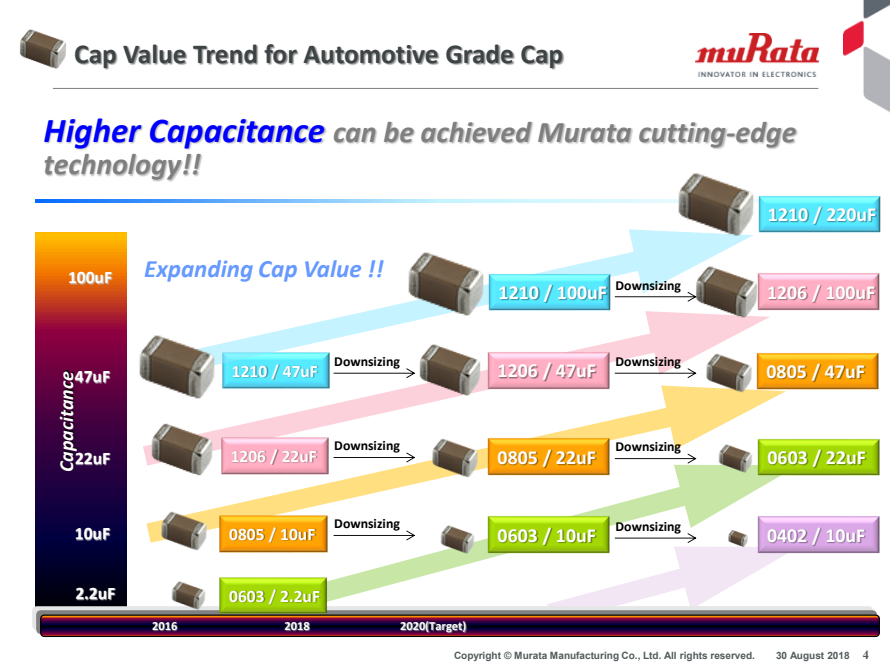

자동차 등급 커패시터 용량 트렌드 (Cap Value Trend)

• 주제: 무라타의 첨단 기술을 통해 달성되는 용량 값 확대 및 소형화.

• 내용: 2016년부터 2020년 목표까지 MLCC의 고용량화 및 소형화 추세를 보여줍니다. 예를 들어, 1206 사이즈에서 22µF (2016)가 47µF (2018)를 거쳐 100µF (2020 목표)로 확장되는 추세입니다.

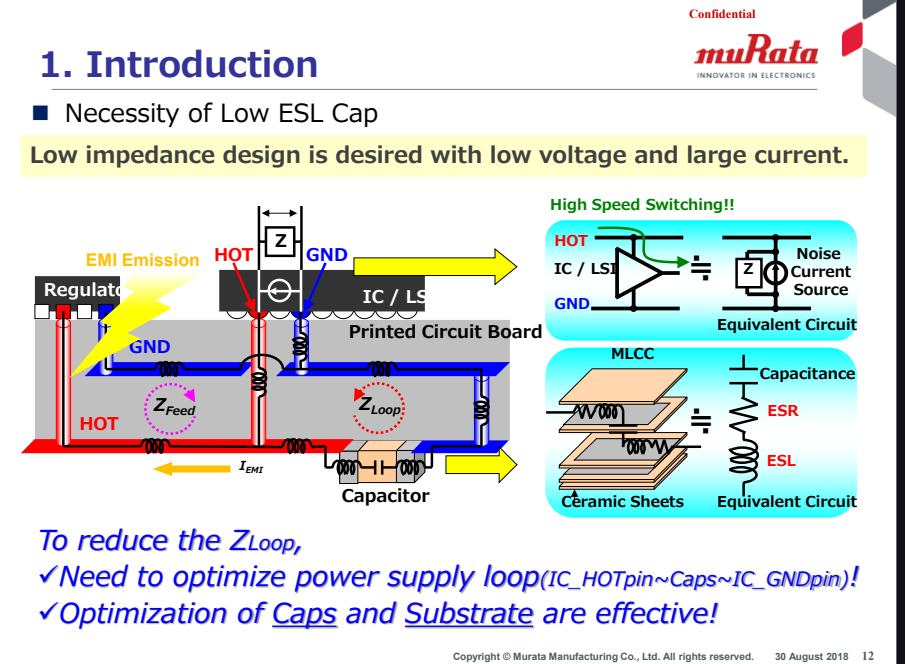

Low ESL 커패시터의 필요성

• 주제: Low ESL 커패시터가 필요한 이유.

• 배경: IC/LSI 회로가 저전압 및 대전류 환경에서 고속 스위칭을 수행하므로 저 임피던스 설계가 요구됩니다.

• 해결책: 전력 공급 루프 임피던스 ()를 줄이기 위해 커패시터와 기판을 최적화해야 합니다.

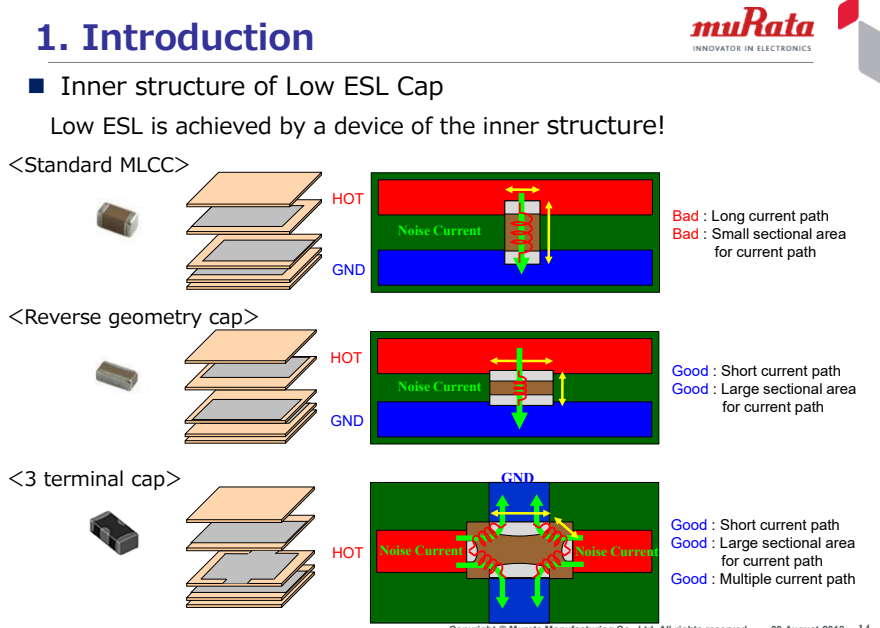

Low ESL 캡 최적화 및 내부 구조

• 주제: Low ESL 커패시터 활용을 통한 최적화 방안 및 내부 구조 설명.

• 효과: 저 임피던스, 수량 감소, 면적 감소, 비용 절감을 달성.

• ESL 비교: 3단자 커패시터는 표준 MLCC의 약 1/10 수준의 ESL을 가지며, 역 기하학적 커패시터는 약 1/3 수준의 ESL을 가집니다

구조: Low ESL은 짧은 전류 경로, 넓은 단면적, 다중 전류 경로를 갖는 내부 구조 설계를 통해 달성됩니다

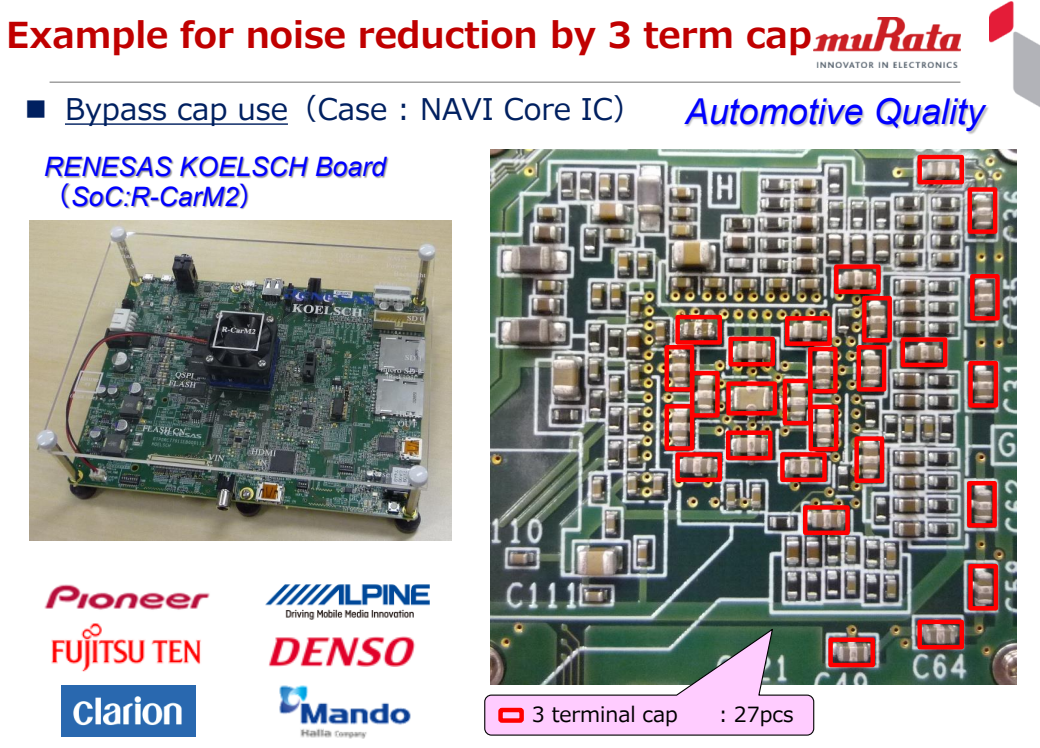

3단자 커패시터 사용 예시 및 시뮬레이션 방법

• 주제: 3단자 커패시터의 필터 및 바이패스 사용 예시와 시뮬레이션 방법.

• 3단자 캡 사용: 필터 용도(Feed thru usage)와 바이패스 캡 용도(Non-feed thru usage) 모두에서 우수한 성능을 보입니다.

◦ 바이패스 캡으로 사용 시 (HOT과 GND 사이에 4점 병렬 연결), 내부 전자기 간섭(IEMI)의 일부가 3단자 캡을 통과하지 않아 가장 작은 Z_{Loop}와 가장 작은 IEMI를 제공합니다.

• 시뮬레이션 방법: 전자기장 시뮬레이터 **"SIwave 2018.0"**를 사용하여 멀티포트 S-파라미터를 계산하고, 이를 커패시터의 S-파라미터와 결합하여 루프 임피던스 () 시뮬레이션을 실행합니다

'Product' 카테고리의 다른 글

| (2020) Low-ESL MLCCs by SEMCO (0) | 2025.10.27 |

|---|---|

| (2012) Murata Technology for commodification of small size MLCC with high capacitance for Space Application (0) | 2023.05.29 |

| (2015) Murata MLCC promotion (0) | 2023.05.29 |

| (2020) 전장용 MLCC 기술전망 (삼성전기 정해석 개발팀장) (0) | 2023.05.29 |

| (2021)TDK의 테크놀로지 Vol 4. MLCC와 미세구조 제어 (0) | 2023.05.28 |