| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

- C0G

- Zirconia

- X7T

- hydrothermal

- CSZT

- X8R

- nano powder

- coating

- Automotive

- Murata

- nickel

- halt

- ni-paste

- ASSB

- mlcc

- Sintering

- core-shell

- paste

- NI-MLCC

- oxygen vacancy

- bme

- BaTiO3

- Powder

- ZrO2

- CERAMIC

- dispersion

- Barium titanate

- microstructure

- reliability

- EV

- Today

- Total

MLCC Material & Process

Decoupling condensor의 Innovation by TDK 본문

https://product.tdk.com/ja/techlibrary/developing/tfcp/index.html#top

デカップリング・コンデンサのイノベーション LSI直下の基板内に最短距離で一括内蔵 | TDK Develo

極限の省スペース化が求められる電子機器では、近年、LSIのパッケージ基板の内部(厚み)まで有効活用しようという動きが高まっています。TDKの薄膜コンデンサ(TFCP)は、デカップリング用に

product.tdk.com

배경

반도체 제조 프로세스의 미세화는 마이크로프로세서나 메모리, FPGA, 시스템LSI 등 디지털 LSI의 고속화·고주파화를 추진하여 ICT 사회의 발전을 견인해 왔습니다.반면 LSI 구동전압의 저전압화로 공급되는 전원전압에는 고도의 PI(파워 인테그리티:전원의 품질)가 요구되게 되어 있습니다.전원 라인의 전압 변동은 회로를 불안정하게 하여 오동작을 일으키거나 노이즈를 증대시킬 우려가 있기 때문입니다.

그 대책으로서 전원 라인과 그랜드 사이에 콘덴서가 다수 접속됩니다(그림 1).LSI에 흐르는 전류량이 급격하게 변화한 경우에도, 콘덴서에 축적된 전하에 의해서 전압 변동을 억제하는 것과 동시에, 노이즈의 원인이 되는 교류 성분을 그라운드 측에 바이패스 합니다.이것을 디커플링이라고 합니다.즉 LSI측에서 본 전원라인과 그랜드간의 임피던스를 가능한 한 작은 값으로 억제함으로써 PI향상을 도모하고 있습니다.

콘덴서의 교류의 통과용이성은 교류 주파수와 콘덴서의 정전 용량으로 결정됩니다.주파수가 높아질수록, 또 정전 용량이 클수록 통과하기 쉬운 성질이 있습니다.단, 콘덴서에는 리드선이나 전극 등이 갖는 회로도에는 나타나지 않는 인덕터 성분이나 저항 성분이 있습니다.이것을 ESL(등가직렬인덕턴스), ESR(등가직렬저항)이라고 합니다.

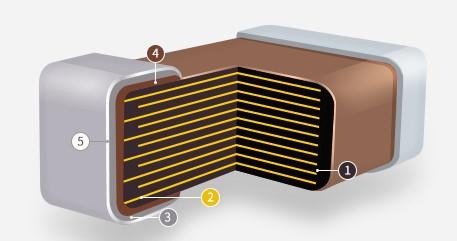

디커플링에서는 넓은 주파수 범위에서 교류 성분을 감쇠시키기 위해 통상 여러 개의 콘덴서를 조합하여 병렬 연결됩니다.저주파 교류성분인 바이패스에는 전해 콘덴서 등 대용량의 콘덴서가 사용되지만 고주파 영역에서는 임피던스를 낮추기 위해 ESL이나 ESR이 작은 콘덴서가 요구됩니다.따라서, 고주파 영역의 디커플링에는 MLCC(적층 세라믹 칩 콘덴서)가 많이 사용됩니다.MLCC는 ESL과 ESR이 작고 임피던스-주파수 특성이 뛰어나기 때문입니다.

디커플링용으로 LSI 주변에 탑재되는 MLCC는 수 10개~100개 안팎에 이르기도 합니다.한편 LSI 패키지의 소형·박형화가 진행되어 MLCC의 탑재 공간 확보가 어려워지고 있습니다.또한 디커플링 콘덴서는 LSI의 전원 단자 근처에서 가능한 한 단거리로 그라운드에 접속하는 것이 원칙입니다.배선로가 분기하거나 연장하면 배선이 가진 ESL이나 ESR에 의해 임피던스가 높아져 디커플링 효과가 저하되기 때문입니다.

그래서 이러한 문제의 유력한 솔루션 중 하나가 LSI를 구현하는 기판 내부의 활용입니다.예를 들어 기판 내부에 캐비티(공동)를 설치하여 얇은 MLCC를 매립하는 방법은 이전부터 채택되어 왔습니다.하지만 적층 공법으로 제조되는 MLCC에서는 두께가 0.1mm 내외가 한계입니다.또, 다수의 MLCC를 기판에 내장시키는 것은 기술적으로도 곤란해, 이득이라고는 할 수 없습니다.TDK는 두께<50um이라고 하는 신개발 플렉시블 박막 콘덴서(TFCP)로 이 과제를 해결합니다.그림 2와 같이 LSI 주변에 배치하던 MLCC를 대신하여 LSI 직하의 기판 내부에 LSI와 최단거리로 내장시키거나 기판 내부의 베어 칩 바로 아래에 매립할 수 있는 시트 형태의 콘덴서입니다.

TDK 소재 기술과 박막 기술이 가능하도록 한 기판 내장에 최적화된 박막 콘덴서(TFCP)

TDK 박막 콘덴서(TFCP)는 유전체의 박막을 2장의 얇은 금속으로 끼운 구조의 콘덴서입니다(그림3).하부전극이 되는 고순도의 니켈(Ni)박에 티타늄산 바륨계 유전체의 박막을 스퍼터링법으로 형성하고 나서 상부전극이 되는 구리를 박막 형성하여 제조됩니다.

TDK에서는 스퍼터링 등의 제조장치도 내제하여 핀홀이나 크랙 등이 거의 없는 양질의 유전체막을 형성함으로써 극히 높은 수율로 시트 형태의 박막 콘덴서를 양산하는 기술을 확립하였습니다.전체 두께는 50μm 이하의 초박형이며 플렉시블한 것이 특징이며 연필 정도의 굵기에 감아도 결함이 발생하지 않습니다.

또, 정전 용량은 1cm2당 1μF로, 지금까지의 상식을 뒤엎는 높은 정전 용량을 실현했습니다.이는 티타늄산바륨계 유전체의 재료설계와 최적화와 스퍼터링 후 아닐(열처리)로 유전체 박막의 고결정화를 촉진하여 종래보다 월등히 높은 비유전율(~1000)을 달성한 데 따른 것입니다.

본 기사에서는 LSI의 디커플링 용도를 중심으로 패키지 기판에 시트 형태로 적층하는 공법에 대해 소개합니다.

인터포저 기판에 다수의 콘덴서 일괄 내장

반도체 디바이스의 고집적화에는 패키징 기술이나 실장 기술이 크게 기여하고 있습니다.반도체 패키지는 외부 환경으로부터 칩을 보호하는 것과 동시에, 프린트 배선판과 전기적으로 접속한다고 하는 중요한 역할이 있습니다.널리 채용되고 있는 FC(플립칩)-BGA(볼 그리드 어레이) 기판 등 LSI에서는 빌드업 기판을 이용한 인터포저가 LSI와 프린트 배선판의 중개역 패키지로 사용됩니다.

빌드업 기판은 코어층이 되는 적층 기판의 상하층에 레이저 등으로 구멍을 뚫어 비아를 형성하고 도금으로 층간을 전기적으로 접속하면서 한 층씩 쌓아가는 공법으로 제조됩니다(코어리스 박형 타입도 있습니다).

빌드업 기판의 인터포저는 일반적으로 1~2mm 정도의 두께로 빌드업층의 층간은 100㎛ 정도밖에 되지 않지만 최근 이 인터포저 기판 내부를 효율적으로 활용하는 기술이 주목받고 있습니다.원래 빌드업 기판은 반도체 제조 기술을 패키지 기판에 응용한 것으로 프린트 배선판(PCB 등)과 비교해 극히 고정밀도로 제조할 수 있기 때문입니다.TDK의 콘덴서(TFCP)는 이러한 선진 요구에 부응하여 완전히 새로운 컨셉으로 개발한 제품입니다.

그림 2에서 소개한 시트형 박막 콘덴서 사진은 내장 콘덴서로 탄생하기 전 제품의 외관으로 인터포저에 내장할 때는 인터포저 제조과정에서 기판에 적층되어 가공되어 다수의 내장 콘덴서로 탄생됩니다. 이것은 이하의 그림 4 에 나타내는 프로세스로 행해집니다.

우선 박막 콘덴서(TFCP)의 시트를 소정의 크기·형상으로 컷 한 후, 하부 전극이 되는 니켈층을 포토 리소그래피로 패터닝합니다.다음으로 절연층을 끼워 기판에 적층하고 나서 상부 전극이 되는 구리층을 패터닝합니다.

여기서부터는 일반적인 빌드업 공법이 됩니다.레이저등으로 절연층에 비아(구멍)를 열고, 도금으로 층간을 전기적으로 접속하는 것과 동시에, 배선 패턴을 후오토리소그래피로 형성해 갑니다.패터닝에는 동박에서 불필요한 패턴을 제거하는 서브트랙티브법과 절연층 위에 구리 패턴을 붙이는 어디티브법이 있습니다.빌드업 기판은 이 두 가지가 이용됩니다.이 공정을 반복함으로써 기판 내부에 다수의 콘덴서를 내장시킨 입체적인 배선로가 구축됩니다.

그림 5와 같이 박막 콘덴서는 LSI 직하의 전원 플레인 및 그랜드 플레인 사이에 형성됩니다.정전용량은 전극의 패터닝을 통해 자유롭게 설계할 수 있고 다수의 콘덴서를 일괄 형성하여 내장할 수 있는 것이 가장 큰 장점입니다.독특한 시트 구조의 박막 콘덴서를 빌드업 공법과 교묘하게 조합하여 내장시키자는 참신한 아이디어로 LSI 바로 아래 인터포저 기판 내에 LSI와 최단거리로 배치할 수 있게 되었습니다.이 때문에, 매우 효과적인 디커플링이 실현됨과 동시에, 패키지 기판의 대폭적인 공간 절약도 가져올 수 있습니다.

LSI 직하의 기판 내장으로 디커플링으로 임피던스를 약 73% 저감

박막 콘덴서의 기판 내장에 의한 디커플링 효과 시뮬레이션 예는 그림 6과 같습니다.

그래프는 ①MLCC를 패키지 뒷면에 표면 실장한 것, ②MLCC를 기판 내에 내장시킨 것, ③박막 콘덴서(TFCP)의 기판 내장 + MLCC의 표면 실장의 각각의 전기 특성을 시뮬레이션한 것입니다.

①의 MLCC 표면 실장에서는 100MHz대의 고주파 영역에 큰 임피던스 피크가 나타나고 있습니다.또, MLCC를 기판내에 내장시킨 ②에서도, 고주파 영역의 임피던스 피크는 반정도로 억제되고 있지만, 충분히 억제되어 있지 않습니다.

정리

TDK의 핵심 기술인 소재 기술과 HDD 헤드 제조 등에서 배양한 박막 기술 등을 구사해 개발한 것이 독특한 시트 모양의 콘덴서인 박막 콘덴서(TFCP)입니다. 2016년부터 양산을 시작해 이미 데이터센터의 서버 등 하이엔드 기기의 CPU 디커플링용 등으로 채택되기 시작했습니다. LSI 직하의 패키지 기판 내에 배치함으로써 소형화·공간 절약이 실현되고, 새로운 고속화·고주파화·전력 절약화를 실현합니다.이에 IoT 시대의 정보량 증대 대응에도 큰 기여를 할 것으로 기대됩니다.

TDK 박막 콘덴서(TFCP)는 시트 구조이기 때문에 다층화로 정전 용량을 증가시킬 수도 있습니다.정전 용량을 증배시킨 제품의 양산 기술은 이미 확립되어 있어 장래적으로는 10배 전후까지의 대용량화를 목표로 해, 새로운 연구 개발을 진행시키고 있습니다.

TDK에서는, 새로운 유전체 재료의 개발이나, 박막 형성 기술의 심화로 다양한 특성을 가진 시트 개발에 임해 가겠습니다.

'Product' 카테고리의 다른 글

| (2021) High Reliability Technology of MLCC for CASE Requirement at Automotive Market (1) | 2022.11.27 |

|---|---|

| 티탄산바륨의 개발역사와 장래전망 (0) | 2022.09.10 |

| (2021) MLCC란 무엇입니까? 공급부족을 해결하기 위한 대체부품과 CASE 진행에 따른 수요예측 (0) | 2022.09.09 |

| 적층세라믹 콘덴서 (전후일본 이노베이션 100선중) (0) | 2022.02.21 |

| (Automotive) Safety MLCC in SEMCO (0) | 2021.11.13 |