| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- EV

- Automotive

- dispersion

- bme

- ZrO2

- nickel

- ni-paste

- NI-MLCC

- Murata

- CERAMIC

- hydrothermal

- X7T

- Barium titanate

- X8R

- core-shell

- Sintering

- coating

- halt

- BaTiO3

- reliability

- microstructure

- mlcc

- CSZT

- C0G

- oxygen vacancy

- nano powder

- Zirconia

- Powder

- ASSB

- paste

- Today

- Total

MLCC Material & Process

(Quality) 세라믹 콘덴서의 신뢰성 본문

9.1 개요

전자회로는 휴대전화, 사무기기, 가전제품 등과 같이 비교적 온화한 조건에서 작동되는 기기 외에도 항공, 우주, 철도, 자동차, 해저케이블, 용광로, 화학 플랜트와 같은 가혹 조건에서 작동하는 설비, 생명과 직접 관계있는 의료기기, 인체에 삽입되는 기기 등 다양한 제품 안에 포함되어 있다. 전자 회로의 사용 환경이나 조건 또한 다양하며, 용도에 따라 전자기기의 설계나 제조, 부품에 요구되는 신뢰성 수준도 다양하다. 교환기, 해저케이블과 같이, 20년 이상 장시간동안 연속해서 정상적으로 작동해야 하는 기기가 있는가 하면, 로케트와 같이 잠깐동안만 정상 작동하면 되는 기기도 있다. 세라믹 콘덴서는 디스크형 뿐만 아니라 적층형도 이들 전자기기의 부품으로 사용되고 있으며, 그 사용환경 및 조건 또한 다양해져 왔다.

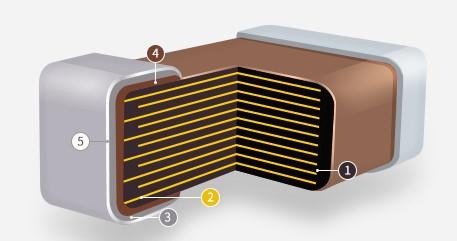

칩형 적층세라믹 콘덴서와 같은 표면실장 대응부품에는 단순히 전기적 신뢰성 뿐만 아니라, 실장 때 가해지는 스트레스를 견디는 내성 및 신뢰성도 중요 한 품질특성중 하나이다. 경박단소(輕薄短小)와 동시에 고기능, 저가격을 요구하는 시장에 대응하기 위해, 최대한의 소형화 및 박층 구조, 대용량 구현을 위한 재료의 개량 및 유전체의 박층화, 비(卑)금속전극 채용에 의한 cost down등 설계에 대한 제약조건이 강화되어 왔다. 전자부품에 요구되는 신뢰성 수준 또한 더욱더 높아져, AQL 보증을 요구하는 수준에서 수 FIT*이하의 시장고장률을 요구하는 수준으로 그 요구가 높아졌다.

이러한 요구에 대응하고자, 세라믹 콘덴서의 제조에서는 강유전체 및 전극재료의 최적화, 가공 정밀도 향상, 산포의 축소, 설계 최적화 등을 통해 신뢰성 을 강화시키는 경향이 지속되어 왔다.

전자기기나 부품의 고장불량은「규정된 기능을 잃어버리는 것」이라 정의할 수 있는데, 성능이 규정치 이하로 떨어짐으로 인해 발생하는 고장과 기기나 부품의 단락, 파괴 등으로 인해 작동이 불가능하게 되어 발생하는 고장으로 크게 구별된다. 사용 시간 경과에 따른 고장 발생 빈도의 모형으로 욕조(bathtub)형 (그림 9.1)이 일반적으로 받아들여지고 있다. 이 곡선은 고장률이 시간 순으로 세 개의 영역으로 구분됨을 보여 주는데, 세라믹콘덴서의 수명도 이 모형과 일치한다.

그림9.1 수명특성곡선(bathtube curve)

[1] 초기고장

초기고장은 제품에 사용하는 소재 및 부품으로의 이물, 불순물, 불량품의 혼입, 제조공정에서의 이물, 불순물 혼입 및 작업실수, 기판실장 때의 과도한 기계적, 열적 스트레스에 의한 damage, 기기 시험 중의 과도한 전기적 damage등의 다양한 원인으로 제품이 제 기능을 발휘하지 못하고 단시간 안에 파손 혹은 기능 저하되는 고장을 가리킨다.

초기 고장을 줄이기 위해서는 세라믹 콘덴서의 개발단계에서 실장시험, 초기고장시험, 수명시험 등을 실시하여 원재료의 선정, 공정설계 및 제품설계의 타당성을 확인해야한다. 또한 양산 단계에서는 제조 공정의 산포나 불량율을 감소시키려는 노력 외에, 제조공정 중의 검사, 또는 제조 완료 후 적당한 조건에서의 각종 전기적 특성(정전용량값, tanδ, 내압시험, 절연저항 등)의 전수 검사를 통해 초기 고장 불량품의 유출을 방지하려는 노력이 강구되고 있다.

[2] 우발고장

우발고장은 사용재료, 부품, 제조공정은 정상이나 어떤 원인 때문에 우발적으로 발생하는 고장을 말하는데, 고장 원인을 특정할 수 없는 경우가 많다. 우발고장 단계는 제품 고장률이 가장 낮게 안정되어 있는 시기로, 이 기간이 제품의 내구수명에 해당한다. 부품 혹은 제품의 사용 전압 혹은 온도를 내려 사용함으로써 고장 발생률을 더욱 억제해, 내구수명을 연장시킬 수 있다. 위성이나 해저 케이블 중계기 등에 사용되는 고신뢰성품에는 0.1FIT이하의 우발고장률이 요구되며, 부품에는 안전계수를 극대화시킨 설계가 적용된다.

[3] 마모고장

마모고장은 부품을 규정 사용조건에서 장시간 계속해서 사용함에 따라, 재료가 서서히 화학적, 물리적 변화를 일으켜 특성이 열화되어 파괴 상태에 이르는 유형의 고장이다. 세라믹콘덴서의 경우, 유전체재료, 전극재료, 외장재료등의 열화에 따라 제품의 전기적 특성이 손실되는 것을 말한다.

제품에 가해지는 온도, 광, 압력, 변형, 전압, 전류 등 고장을 유발하는 스트레스와 특성 열화의 관계를 재료 과학적으로 밝히고, 그 정량적 관계를 파악하는 것이 제품품질보증의 기본이다.

기기가 사용되는 10~20년의 기간보다 마모 수명을 더 길게 설정하는 것이 일반적이다. 세라믹콘덴서는 실제 사용환경에서 매우 안정되게 성능을 유지하여, 기기의 내구년수 안에 마모고장 영역에 이르러 불량을 발생시키는 경우는 없다. 그러나, 사용환경조건이 가혹해짐에 따라 마모고장 개시 시기가 빨라질 수도 있다. 따라서 마모 고장시험으로 수명을 파악하고, 특성 열화의 원인을 밝혀 제품설계나 제조 관리에 반영, 사용 때의 마모고장 발생을 방지하려는 노력이 경주되고 있다.

이상, 개략적으로 신뢰성에 관하여 기술하였다. 세라믹콘덴서의 구성 재료는 안정된 특성을 유지하므로 , 본질적으로 신뢰성 문제는 없으나, 요구 특성을 만족시키기 위해 설계 마진을 줄이는 방향으로 개발이 진행되고 있어, 이후에도 신뢰성 확보를 위해 특별한 배려가 필요하다.

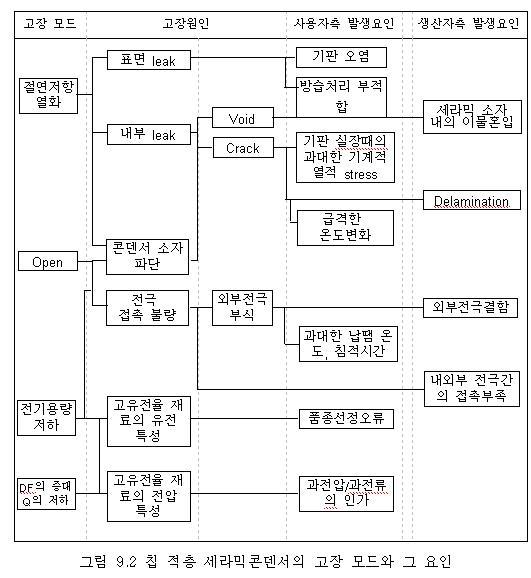

9.2 적층세라믹콘덴서의 고장 모드와 메커니즘

신뢰성시험의 설명에 앞서, 적층세라믹콘덴서의 주요한 고장 모드와 고장 메커니즘에 관해 정리해 두자.

그림 9.2에, 적층세라믹콘덴서의 대표적인 고장 모드와 그 발생 원인을 사용자측 원인과 제조자측 원인으로 구분하여 정리하였다. 세라믹콘덴서의 고장은 세라믹스 소자 중에 발생하는 크랙등의 결함에서 기인한 경우가 많다. 고장 발생을 방지하기 위해 사용자측, 제조자측 쌍방의 연구가 필요하다.

9.2.1 절연저항열화

[1] 전극 migration에 의한 표면 leak

칩 적층세라믹콘덴서는 표면이 노출된 상태로 기판에 부착되므로 이온 migration에 의한 표면 leak에 의해 절연저항이 열화되거나 혹은 단락불량이 발생한다.

Migration의 예를 각각 사진 9.1(a), (b)에 나타내었다. (a)는 칩 표면의 물기를 통해 도금에 사용된 Sn이 칩 표면에서 migration된 예이며, (b)는 방수를 위한 coating재와 칩 표면 사이에서 발생한 Sn의 migration 예이다.

(a) 칩 표면에 물방울이 떨어져 발생한 migration b) 방수제막 아래에 발생한 migration

고온 다습한 상태에서 직류 전압이 인가되면, 외부전극의 금속이 이온화되어 칩 표면을 따라 양극에서 음극으로 이동하여 음극에서 환원 석출된다. 칩 표면의 flux나 그 외의 잔류수화물이 migration을 가속시키는 경우가 있다. 칩 표면이 결로되지 않거나 장시간 고온 다습 조건에 노출되지 않는다면 migration을 염려하지 않아도 된다. Migration 발생 가능성은 Ag>Ag-Pd>Sn>Cu>Ni 순으로 작은데, 특히 migration이 발생하기 쉬운 Ag를 외부전극으로 사용하는 경우, 그 위를 Ni이나 Sn으로 도금하여, Ag가 직접 표면에 노출되지 않도록 해야한다. 도금을 하지 않는 경우는 Pd 10%이상의 Pd-Ag 합금을 사용하여 migration 발생을 방지한다. 최근 내부전극으로 Ni, Cu등의 비금속을 사용하는 경우가 많은데, 이 경우 외부전극으로 Cu가 사용되므로, migration 발생 가능성은 거의 없다.

그러나, 표면이 결로되어 전계에 의한 금속의 이온화가 촉진되는 환경에 칩이 장시간 노출된다면, 어떠한 금속을 사용하더라도 migration 발생은 피할 수 없다.

특히 주의해야 할 점은 사진 (b)와 같이 방수 수지로 표면을 코팅하는 경우, 수지 선택이나 curing 조건이 잘못되면 수지 중의 불순물이나, 수지 내부에 trap된 수분으로 인해, 오히려 migration이 일어나기 쉬운 경우가 있으므로, 수지를 선택할 때 충분한 평가가 필요하다

[2] Void나 Delamination에 의한 절연 열화

칩 내부에 void나 delamination이 존재하면, 내열성이나 기계적 강도가 저하되어 크랙이 발생하기 쉽다. 또한 crack이 발생하지 않더라도, 전압 인가 시 그 부분에 전계가 집중되어, 부분 방전(PD: Partial Discharge)이 일어나 그 부분에서부터 열화가 진행된다.

Void는 원재료나 내부전극의 인쇄, 적층 공정 중에 혼입된 이물이 소성 때 타버리거나 또는 세라믹과 반응함으로써 생기는 빈 공간이다. 사진 9.2는 내부 전극 인쇄 때 이물이 혼입되어 발생한 void의 예를 보여준다.

사진 9.2 이물혼입에 의한 적층세라믹 콘덴서 내부의 void

적층 세라믹콘덴서 제조 공정에서는 원재료의 제조, 조합, 그린시트의 성형, 인쇄 적층 등의 공정을 크린룸 내에 설치하고 경우에 따라 크린부스를 병용함으로써 설비 근처의 청결도를 높여 먼지에 의한 void 발생을 방지하고 있다.

Delamination은 내부전극 두께가 불균일하거나 유전체 및 전극의 일체 소성 시 조건이 부적절할 때, 세라믹과 내부전극의 소성 수축이 다름으로 인해 발생하기 쉽다. (사진 9.14 참조)

[3] Crack에 의한 절연 열화

Crack 발생의 원인은 매우 많다. 콘덴서 제조공정에서의 취급 부적절로 인해 발생하는 경우도 있지만, 칩 콘덴서의 경우는 기판 실장 때의 스트레스 때문에 crack이 발생하기도 한다. Crack이 칩의 내부 전극 근처에서 발생하면, 그 부분의 내부전극 사이에서 leak가 발생하여 쇼트되기 쉽다. 외부에서 관찰되는 crack은 선별 가능하나 내부 crack은 선별이 불가능하여 시장에 출하될 경우, 사용 중에 쇼트 또는 IR low의 문제를 일으킨다.

실장 때 crack을 발생시키는 원인은 기계적 스트레스에 의한 것과 열적 스트레스에 의한 것 등 두 가지로 나뉘어진다.

열적 스트레스는 주로 납땜시에 받는데, 예열 온도와 납땜 온도의 온도차가 너무 크거나, 납땜 후의 냉각 속도가 너무 빠르면 crack이 발생하기 쉽다.

또 한 납땜 인두를 사용하는 경우, 인두 팁의 온도 관리나 직접 팁이 칩에 닿지 않도록 주의해야 한다. 열스트레스 때문에 발생한 crack은 내부전극에 평행하게 발생하는 경향이 있다. (사진 9.3)

사진 9.3 적층세라믹콘덴서의 열충격 crack

실장 때의 기계적 스트레스 때문에 발생하는 crack으로 다음과 같은 것들이 있다.

① 실장기의 흡착 노즐의 충격으로 발생하는 crack (사진 9.4)

흡착 노즐의 하사점(칩을 기판에 내려놓는 위치)이 너무 낮아 칩에 과대한 스트레스가 가해지면 crack의 원인이 된다. 얇은 칩에서 발생하기 쉬우며, crack은 칩 중앙 부근에서 발생한다. 칩 두께에 맞는 적정 높이 설정이 필요하다.

사진 9.4 흡인 노즐에 의한 crack

② 위치 결정 척(chuck)의 충격에 의해 발생하는 crack (사진 9.5)

최근의 실장기는 이러한 충격이 가해지지 않도록 화상 인식으로 위치를 결정하는 방식을 채용하는 추세이나, 이전 설비는 기계적으로 위치를 결정하는 경우가 있는데 충격력을 억제하도록 위치 결정 chuck을 관리해야 한다. chuck에 의한 crack에는 칩 내부에 발생하는 것과 표면이 조개 껍질처럼 벗겨지는 쉘 crack등이 있다.

사진 9.5 위치결정 척의 충격에 의한 crack

③ 기판의 휨 응력에 의해 발생하는 crack (사진 9.6)

납땜 후에 기판을 과도하게 휘면 칩이 깨지는 경우가 있다. 기판 실장 후에 발생하는 crack으로 가장 발생 빈도가 높은 것이 이러한 기판 휨에 의한 crack이다. 기판이 휘는 원인은 많은데, 전 공정에 걸쳐 기판이 과도하게 휘어지지 않도록 하는 관리가 중요하다. 기판 휨에 의한 crack은 기판과 맞닿는 외부전극의 선단부터 칩 내부로 진행되므로, 외부에서 발견하기 어렵다.

사진 9.6 기판 휨에 의해 발생한 crack

④ 납땜의 응력에 의한 crack (사진 9.7)

과량의 납땜은 납의 수축 때나 기판이 휠 때, 보다 큰 스트레스의 원인이 되어 crack을 발생시키기 쉽다. 납땜의 양이 적당하도록, 랜드의 치수 조절이나 솔더 레지스터 인쇄로 랜드 노출면을 조절하는 등의 노력이 필요하다. 특히 flow 방식의 납땜의 경우는 이러한 납땜 량 과다가 발생하기 쉽다.

사진 9.7 납땜 과다로 발생한 crack

⑤온도 사이클에 의해 발생하는 crack (사진 9.8)

알루미늄 금속기판과 같은 열팽창율이 큰 기판에 실장된 경우, 세트 동작때 기판의 열팽창 수축에 의한 스트레스로 crack이 발생하기 쉽다. 사진은 칩을 유리 에폭시 기판에 실장하여, 욕조 중에서 -55℃와 125℃ 사이를 1000번 왕복하는 열충격 시험을 실시한 경우 발생한 crack이다. Crack은 기판 휨에 의해 발생하는 crack과 비슷한 모양으로, 외부전극 선단부로부터 칩 내부를 향하여 진행하나, 기판과 접하지 않는 칩 윗면에서 발생하는 것이 특징이다.

사진 9.8 온도사이클 시험으로 발생한 crack

'Process' 카테고리의 다른 글

| (MLCC)환원성 분위기하에서의 유전체 소성 (0) | 2021.04.03 |

|---|---|

| (MLCC)X7R 특성 적층 세라믹 콘덴서 재료의 소결 중 미세구조 변화 분석 (0) | 2021.04.03 |

| (Quality)고온가속수명 (0) | 2021.04.03 |

| (Sintering) Rack 소성 시스템 (0) | 2021.04.03 |

| (De-bindering)탈바인더 기술과 그 최적화 (0) | 2021.04.03 |