2022. 8. 6. 21:02ㆍ2004-알기쉬운 칩부품의 제조공정

3-5 콘덴서의 기본 설계

콘덴서의 용도는 매우 다양합니다. 콘덴서는 면적이 클수록, 유전체 층이 얇을수록, 비유전율이 클수록 용량값이 커집니다. 응용 면에서 볼 때, 고주파에서는 용량이 작아도 Q가 높은 콘덴서가, 전원용에서는Q는 작아도 대용량의 콘덴서가 필요합니다. (그림 3.10)

고주파용 콘덴서로의 대응

고주파용 콘덴서에서는, 인피던스 매칭 등 고주파 회로에서의 신호처리가 주요 업무입니다. 이를 위해서는 소용량, 저 ESR, 저 ESL, 고정밀도, 소형, 그리고 주파수 특성이 좋은 것이 필요합니다. 고주파용으로, 대용량값은 그다지 필요하지 않습니다. 이 목적에 적합한 콘덴서로서, 온도보상용의 칩 세라믹 콘덴서, 저손실 유전체를 사용한 Q 가 높은 칩 세라믹 콘덴서 및 필름 콘덴서가 있습니다.

전원용 콘덴서로의 대응

전원용 콘덴서에서는, 교류에서 직류로의 정류, 또는 직류에서 직류로의 변환이 주요 업무입니다. 이를 위해서는 대용량으로 저 ESR 및 저 ESL로, 저유전체 손실과 대전류 대응의 콘덴서가 필요합니다. 일반적으로 정밀도는 필요하지 않습니다. 그러나 동작속도가 고속화되어, 고주파 특성이 요구되고 있습니다. 이 목적에 적합한 콘덴서로는 알루미늄 전해 및 칩 세라믹 콘덴서 등이 있습니다. 그 외에 탄탈 콘덴서 및 OS(Organic Semiconductor: 유기 반도체) 콘덴서 등이 있습니다.

3-6 제조전 준비

3-6-1 콘덴서에 필요한 주변 기술

칩 세라믹 콘덴서를 만들기 위해서는 목표로 하는 성능의 이미지를 명확하게 하고, 이를 바탕으로 제조하기 위한 주변 기술을 준비하는 것이 필요합니다. (그림 3.11) 칩 세라믹 콘덴서에 사용되는 세라믹 재료에 대해서 살펴 보겠습니다.

목표로 하는 칩 세라믹 콘덴서

칩 세라믹 콘덴서는 유전체로 된 매우 얇은 세라믹 기판에 전극을 인쇄에서 형성하고 적층하여, 소성하고 일체화한 구조입니다. 이 때문에 Monolithic(일체형) 콘덴서라고도 불립니다. 병렬접속으로 인해 소형으로 대용량을 얻을 수 있습니다.

칩 세라믹 콘덴서의 특징은 소형・각형으로 장착성이 좋고, ESR 및 ESL이 작고, 고주파 특성이 뛰어나며, 양단의 전극을 직접 납땜할 수 있는 표면실장 구조라는 점입니다. 이 적층형 칩 세라믹 콘덴서의 칩 사이즈는 규격화되어, 3216 (L3.2mm×W1.6mm×t1.6mm) 이나 0603 (0.6mm×0.3mm×0.3mm) 등이 개발되고 있습니다.

칩 세라믹 콘덴서를 만들기 위해 필요한 기본 주변 기술

칩 세라믹 콘덴서를 만들기 위해 필요한 기본 주변 기술은 3가지 정도 있습니다.

* 세라믹 그린 시트: 이것은 칩 세라믹 콘덴서를 만들기 위한 기판입니다. 여기에 는, 순도가 높은 세라믹 기판이 주로 사용됩니다. 여기에서는, 열팽창 계수 및 열전도성, 기계적 강도에 대해서 고려할 필요가 있습니다.

* 인쇄 페이스트: 이것은 칩 세라믹 콘덴서의 외부전극을 형성하고 내부전극을 형성하기 위한 인쇄용 페이스트 입니다. 칩 세라믹 콘덴서의 성능을 좌우하는 중요 한 재료로, 등가직렬 저항 등의 점을 고려할 필요가 있습니다.

* 스크린 마스크 작성 : 칩 세라믹 콘덴서를 만들기 위한 전극 구조, 배선도체 및보호막 형성용의 인쇄용 스크린 마스크 입니다.

칩 세라믹 콘덴서의 성능 목표

콘덴서의 용도는 매우 다양합니다. 콘덴서의 성능목표는 용량치 정밀도가 좋고, 등가직렬 저항이 작고, tanδ 이 작고, 고주파 특성이 좋고, 소형으로 안정성이 높으며 실장이 확실하게 되도록 하는 것입니다.

3-6-2 세라믹 그린 시트의 제조

여기에서는, 칩 세라믹 콘덴서의 기본이 되는 유전체 재료의 준비부터 슬러리 제조까지의 내용에 대해서 살펴 보도록 하겠습니다. (그림 3.12)

* 유전체 재료의 준비: 칩 세라믹 콘덴서의 종류로는, 온도 보상계 및 高유전체계(대용량용) 등이 있습니다. 여기에서는 高유전체계에 대해 살펴 보겠습니다. 이 세라믹을 제조하기 위한 재료는 티탄산 바륨 BaTiO3으로, 이 원료는 유전체 재료인 탄산 바륨 BaCO3 및 산화 티탄 TiO2, 첨가물 등의 분말입니다. 이 재료로 일반적으로 고상법에 의한 제조 방법으로 세라믹을 만들어 갑니다. 칩 사이즈1608(1.6mm×0.8mm) 로 용량값 10μF 이상의 대용량 칩 세라믹 콘덴서를 만들려면, 얼마나 유전체 두께를 얇게 만드느냐가 가장 중요한 열쇠가 됩니다. 세라믹 그린 시트의 두께로는 10~1μm 정도가 가능해 졌습니다. 이렇게 얇게 만들기 위해서는, 분말입자의 입경은 0.5μm 이하로 하고, 또한 분말 분자의 입경을 균일하게 해야 합니다.

* 원료의 조합・가소성 : 콘덴서용 원료는 탄산 바륨 BaCO3와 산화 티탄 TiO3의 소재가 되는 분말 원료와 특별한 첨가제를 준비하고, 여기에 물을 넣으면서 잘 섞어 조합합니다. 이렇게 한 다음 기포를 빼면서 충분히 건조시키고, 열을 가하여 가소성합니다.

* 원료의 분쇄・건조 : 가소성하면 티탄산 바륨 BaTiO3이 만들어 집니다. 가소성한 원료는 건조하고, 분쇄하여 미립자화 합니다. 이렇게 하여, 미립화된 유전체 분말을 얻을 수 있습니다. 이것이 칩 세라믹 콘덴서의 유전체 원료입니다.

* 슬러리의 제조 : 이 유전체 분말에 유기 바인더 및 용제가 첨가 됩니다. 유기 바인더의 역할은 성형조제 및 분산제입니다. 이것을 볼 밀 등으로 분쇄하고, 혼합합니다. 혼합 시 기포가 생기기 쉬우므로 감압하여 실시합니다. 이것이 진흙 상태의 슬러리가 됩니다. 이것이 세라믹 그린 시트의 원료입니다. 이것을 다이코터법이나 닥터 블레이드법 등으로 캐리어필름 위에 얇게 펴줍니다. 이것을 건조시키면 얇은 세라믹 그린 시트가 완성됩니다.

3-6-3세라믹 그린시트의 종류

칩 세라믹 콘덴서를 만들기 위해서 필요한 재료가, 유전체의 세라믹 그린 시트입니다. 유전체에는 유전율이 10~200까지의 상(常)유전체와 1000~20000까지의 고유전체 재료의 2종류가 있습니다. (그림 3.13)

상(常)유전체계의 세라믹 그린 시트

온도 보상용으로 상유전체인 티탄산 마그네슘 MgTiO3 및 티탄산 칼슘 CaTiO3 등의 재료를 사용합니다. 유전율은 약 400이나 조성성분에 따라 변경될 수 있습니다. 온도 보상이란, 사용하는 온도 변화에 대해서 용량값이 직선적인 정전용량 온도계수를 가지는 것입니다. 이 특성은 C△특성(0±△ppm/℃), SL특성(+100~1000ppm/℃)으로 나타내었습니다.

주로 사용되는 C△특성은 CG특성(정전용량 온도계수 C특성으로 0ppm/℃, 허용차 ±30ppm/℃) 및 CH특성(C특성으로 0ppm/℃, 허용차 ±30ppm/℃) 등으로 나타내었습니다. 이것은 저항기 및 인덕터 등의 온도계수를 보상하도록 되어 있습니다. 사용하는 세라믹 재료는, Q=1/tan이 높고, 유전손실이 작다는 특징을 가집니다. 이것은 고주파 회로용에 적합합니다.

고유전율계의 세라믹 그린 시트

여기에는 고유전체인 티탄산 바륨 BaTiO3등의 재료를 사용합니다. 유전율이 상온에서 1600으로 높으므로, 소형으로 대용량의 콘덴서를 만들 수 있습니다. 온도 특성은 큰 값을 나타내고, 정전용량 변화율로 B특성 및 F특성 등이 있습니다.

그러나, 이 세라믹 재료에는, Q가 작고, 손실이 크며 유전체의 온도 변화 및 경시변화가 있으며, 직류 전압에 의존하고 용량값이 변하기 쉽다는 결점이 있습니다. B특성(-25℃~ +85℃로 정전용량 온도 계수±△10%), F특성(-25℃~+85℃로 정전용량 온도계수+30/-80%)이 있습니다. 이 때문에, 큰 진폭 동작에서는 왜곡이 발생하기 쉬우므로, 이 응용 분야에서는 필름 콘덴서가 적합합니다. 강자성(强磁性) 세라믹은 경시변화를 합니다. 도메인(결정 분자가 갖추어진 영역)이 시간의 경과함에 따라 이동 하고, 비유전율이 저하되기 때문입니다. 이 도메인은 강(强)자성체와 상(常)자성체의 상전이하는 큐리 온도 이상으로 가열하면 원래의 비유전율 상태로 회복합니다.

3-6-4 인쇄 페이스트와 스크린 마스크

칩 세라믹 콘덴서에는 내부전극과 외부전극이 있습니다. 전극용 페이스트재는 이 내부전극 형성과 외부전극 형성을 위해서 사용합니다. (그림 3.14) 스크린 마스크는 내부전극 형성과 외부전극 형성의 스크린 인쇄용입니다.

내부전극용

칩 세라믹 콘덴서의 성능을 좌우하는 요인의 하나로 등가직렬 저항 ESR이 있습니다. 즉, 이 ESR을 작게 하는 것이 성능향상으로 이어집니다. 칩 세라믹 콘덴서는, 세라믹 그린 시트 표면 각각에 평면전극을 형성합니다. 이것이 내부전극입니다. 이 구조는 얇은 세라믹 그린 시트를 적층하고 표면적을 넓힙니다. 마지막으로 각각의 세라믹 측면전극을 모아서 접속할 필요가 있습니다. 이것이 외부전극입니다. 이 내부전극의 저항값이 증가하면, ESR이 나빠집니다. 이 내부전극 페이스트에는, 유전체에 티탄산 마그네슘 MgTiO3을 사용하는 경우에는, 팔라듐 Pd 및 은/ 팔라듐(Ag/ Pd) 등이 사용됩니다. 최근 더욱 다층화가 진행되어, 저(低)저항화를 위해 니켈 Ni 및 구리 Cu 가 주목 받고 있습니다.

외부 전극용

외부전극 단자는 2개 있습니다. 이 외부전극은, 각각 쌓아 올린 다층의 내부전극을 병렬로 접속하기 위해서 사용합니다. 이 외부 전극은 일반적으로 귀금속인 팔라듐 Pd 및 은/ 팔라듐(Ag/ Pd) 등의 전극 페이스트를 적층 측면에 도포하고, 소성하여 형성합니다. 전극용 페이스트의 재료로는 비저항값이 작고, 최적의 접착강도를 지니며, 마이그레이션에 우수한 특성이 있으며 파인패턴이 가능한 등의 부분을 포인트로 하여 선정합니다. 가격 문제로, 외부 전극은 귀금속에서 구리 등의 비금속으로 바뀌고 있습니다.

스크린 인쇄기술

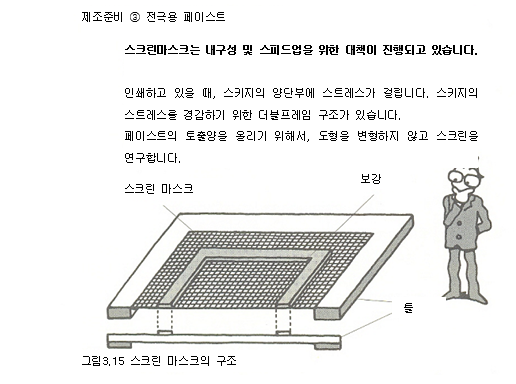

세라믹 기판상에 내부전극과 외부 전극용 페이스트를 스크린 인쇄하기 위해서, 스크린 마스크가 필요합니다. (그림 3.15)

3-7. 칩 세라믹 콘덴서의 제조

3-7-1 칩 세라믹 콘덴서의 제조 Flow

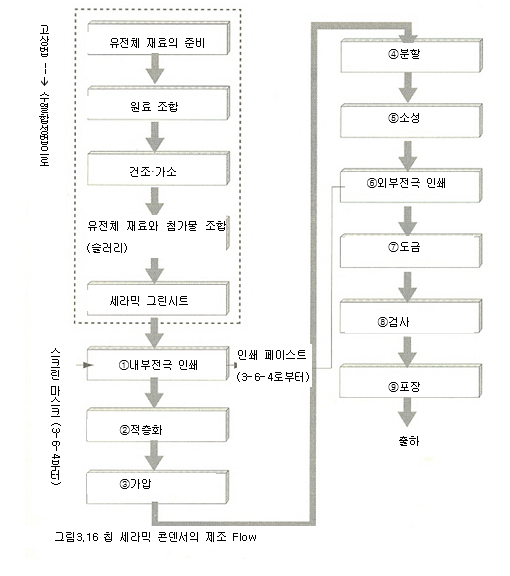

칩 세라믹 콘덴서를 제조하기 위해서 필요한 것이 제조 Flow 입니다. 여기에서는, 이미 준비한 세라믹 그린 시트와 인쇄 페이스트, 스크린 마스크를 사용합니다.

제조 Flow

칩 세라믹 콘덴서를 제조하기 위해서는, 대체적인 제조 Flow가 필요합니다. 여기에서는 이미지적인 제조 Flow를 그림 3.16 에 나타내었습니다.

* 세라믹 그린 시트 준비: 슬러리를 시트 성형기로 세라믹 그린 시트로 만듭니다.

이것이 칩 세라믹 콘덴서의 가장 기본이 되는 재료입니다.

* 내부 전극 인쇄: 세라믹 그린 시트상에 내부전극을 인쇄하는 공정입니다.

* 적층과 Press: 내부전극을 인쇄한 세라믹 그린 시트를 겹쳐서 프레스로 가압하고, 일체화하는 공정입니다.

* 분할: 적층한 세라믹 그린 시트를 칩 크기대로 분할해 갑니다.

* 단면 전극 인쇄・소결: 칩으로 만든 측면에 도체를 인쇄하고, 소성하는 공정입니다.

* 외부전극 도금: 측면에 도체를 단 칩 전극에 Ni과 Sn을 도금하는 공정입니다.

* 검사: 도금 처리가 끝난 칩의 전기적 특성을 체크하는 공정입니다.

* 포장: 테이프 릴에 완성한 칩 세라믹 콘덴서를 채워 넣습니다.

* 출하: User에게 출하합니다.

칩 세라믹 콘덴서를 제조하기 위해서는, 제조 Flow의 바탕이 되는 많은 주변 기술에 대한 준비작업이 필요합니다. 이 주변 기술의 도움이 있어야, 비로소 칩 세라믹 콘덴서의 제조가 가능해 집니다.

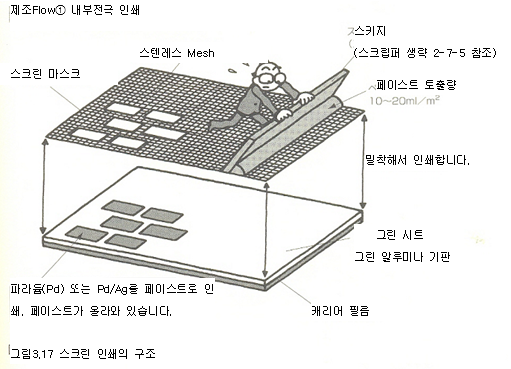

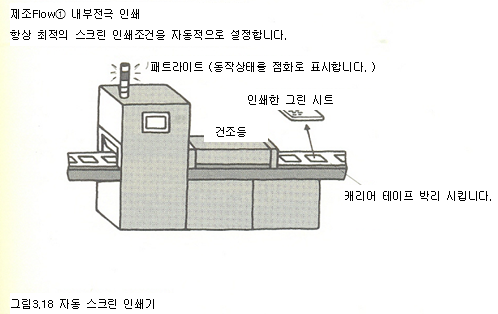

3-7-2 내부전극 인쇄

여기에서는, 세라믹 그린 시트상에 내부전극을 인쇄하는 공정에 대해서 알아보겠습니다. (그림 3.17, 그림 3.18)

* 세라믹 그린시트: 세라믹 그린 시트는 진흙 상태로 슬러리화 된 세라믹 유전체를 다이코터법 및 닥터 블레이드법 등에 의해 PET(Poly ethylene terephthalate) 필름 등으로 만들어진 케리어 필름상에 얇게 펴서 만듭니다. PET 필름의 특징은 소재가 튼튼하고, 표면고유 저항값이 106Ω/cm 으로 높고, 고도의 대전방지 성능이 있다는 점입니다. 이것을 시트 성형기로 건조시킨 것이 세라믹 그린 시트입니다. 하얗고 부드럽고, 얇은 판상입니다. 식별을 위해서 세라믹 그린 시트에 엷은 색을 입히는 경우가 있습니다.

* 내부전극 인쇄: 칩 세라믹 콘덴서의 첫 공정은, 내부전극을 인쇄하는 것입니다. 일단, 세라믹 그린 시트에 스크린 인쇄로 내부전극을 인쇄합니다. 이 때 내부전극 인쇄의 위치 정밀도가 매우 중요합니다. 그리고, 이 때문에 많은 연구가 집중되고 있습니다. 다음은 건조시킨 후, 캐리어 테이프에서 세라믹 그린 시트를 박리합니다. 내부전극용 페이스트로 등가직렬저항 ESR의 원인이 되는 접촉저항을 낮추기 위해서 비저항이 작은 귀금속인 팔라듐 Pd 및 은/팔라듐 (Ag/Pd) 이 주로 사용됩니다. 그러나, 유전체가 얇아짐에 따라서 한층 더 저항값을 낮춰야 할 필요가 있어, 니켈 Ni 및 구리 Cu(비저항 Pd: 10.7μΩcm , Cu: 1.67μΩcm) 등이 사용되게 되었습니다. 비금속 니켈 Ni은 융점이 높고, 비저항이 작다는 특징이 있습니다. 그러나, 공기중에 열을 가하면 산화가 진행되므로, N2가스에 의한 환원성 분위기 로가 필요하게 됩니다. 구리는 저(低)손실로 고주파용입니다.

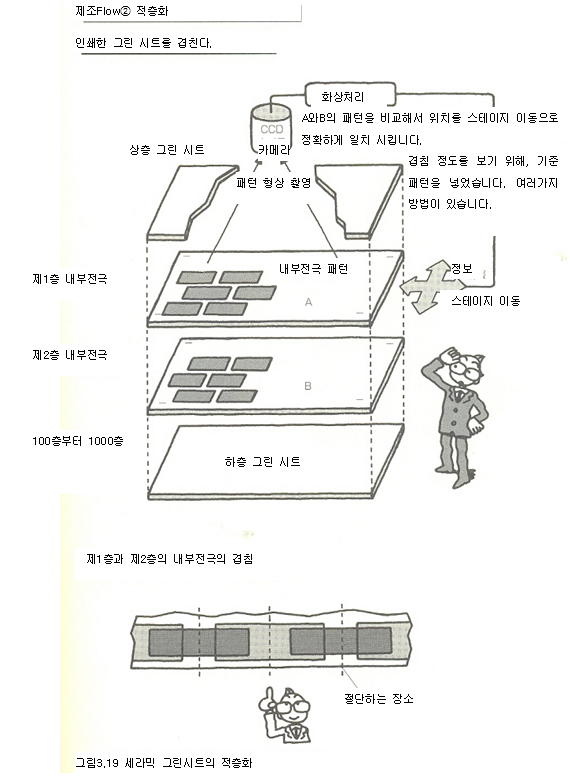

3-7-3 적층화

칩 세라믹 콘덴서를 만드는데 있어서 중요한 것은 내부전극을 형성한 얇고 부드러운 세라믹 그린시트 100층~1000층을 어떻게 하여 정밀도 좋게 적층화 하는가 하는 것이다. (그림 3.19)

* 적층화에 대해서: 내부전극을 인쇄한 사각 수백 mm 크기의 세라믹 그린 시트를 쌓아 갑니다. 이것은 얼핏 보면 간단해 보이지만, 매우 어려운 기술을 필요로 합니다. 여기에서 단순하게 2장의 세라믹 그린 시트를 겹쳤다고 합시다. 세라믹 그린 시트는 흰색(색을 고의로 입히는 경우도 있다.)으로 완전히 불투명하기 때문에, 1층째의 세라믹 그린 시트의 상태를, 2층째에 겹친 세라믹 그린 시트 상에서 보는 것은 불가능하다.

* 정밀도 좋게 겹치려면: 이 잘 겹쳐지는 정도가 칩 세라믹 콘덴서의 용량값을 크게 변화시키며, 잘 겹쳐지지 않을 경우 성능을 열화 시키는 원인이 되기도 합니다. 가령, 이 때의 위치를 맞추는 방법으로 1층째의 세라믹 그린 시트의 한쪽 끝에 표시를 해 두고, 이것을 기준으로 2층째의 세라믹 그린 시트를 겹치는 방법이 있습니다. 이것은 단순한 방법입니다만, 칩 사이즈의 미세화와 함께 큰 오차가 생겨, 미세화 기술에 있어서는 실용적이지 않게 되었습니다.

* CCD 카메라에 의한 방법: 미세화와 함께 주목 받고 있는 방법이 세라믹 그린 시 트상의 패턴 모양을 이용하여 위치를 맞추는 방법입니다. 이 방법은 CCD(Charge Coupled Device: 전하결합소자) 카메라를 이용하여 1층 째의 세라믹 그린 시트상에 표시된 여러 점을 기록하고, 2층째의 세라믹 그린 시트상에 표시된 여러 점과 일치하도록 고정된 1층째에 대해서 2층째를 이동시키면서 정확하게 맞추는 방법입니다. 화상처리 기술과 피드백에 의한 미소(微少)이동 기술이 이 위치결정 방법을 가능하게 하였습니다.

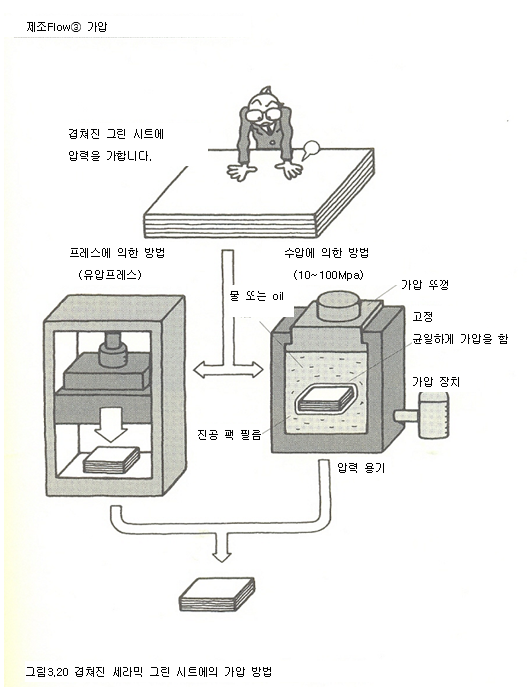

3-7-4 가압

100층~ 1000층 정확하게 겹쳐진 세라믹 그린 시트는, 가압에 의해 압축하는 공정에 들어갑니다. 이 공정에서는 정확하게 균일하게 압축해 주지 않으면, 세라믹 그린 시트상에 위치 틀어짐 등이 남게 됩니다. 이것이 완성된 칩 세라믹 콘덴서의 특성에 커다란 영향을 끼치게 됩니다.

* 가압에 대해서: 이 공정은 내부전극을 형성한 사각 수백mm×수백mm 크기의 얇은 세라믹 그린 시트 100층~ 1000층 정도를 정확하게 정밀도 좋게 압축하여 일체화 하는 것입니다. 여기에서 중요한 포인트는 얼마나 가로, 세로, 높이 방향 (3차원적) 모든 것에 대해서 균일하게 압축하여 가느냐 하는 것입니다. 일반적으로 압축하는 방법으로는 유압 프레스가 사용되고 있습니다. 이 방법은 간단하지만, 3차원적으로 균일하게 압축하는 것은 현실적으로 꽤 어렵습니다.

* 수압・유압을 이용한 방법: 이것은 먼저 압력 용기의 내부에 적층한 세라믹 그린 시트를 두고 가압 뚜껑을 닫고, 다음에 물 또는 기름을 이용하여 가압하는 방법입니다. (그림 3.20) 이 때의 수압 또는 유압은 수십Mpa (메가 파스칼)에서 수백Mpa 정도를 가해 줍니다. 세라믹 그린 시트는 진공 포장 등으로 보호되어, 물 또는 기름이 세라믹 그린 시트 내에 침투하지 않도록 되어 있습니다. 이 방법의 특징은, 매우 균일한 가압을 세라믹 그린 시트에 가하는 것이 가능하다는 것입니다. 이 방법은 세라믹 그린 시트상에 위치 틀어짐 등이 생기지 않습니다. 압력을 가한 세라믹 그린 시트는 약 60% (실제로는 가로 세로 다름)로 수축합니다. 인쇄한 전극 페이스트는 그린 시트 내에 침투하고, 평탄해 집니다.

* 파스칼 Pa: 파스칼은 압력의 단위입니다. 1파스칼은 1m2 당 1뉴튼의 힘이 작용 하는 압력입니다.

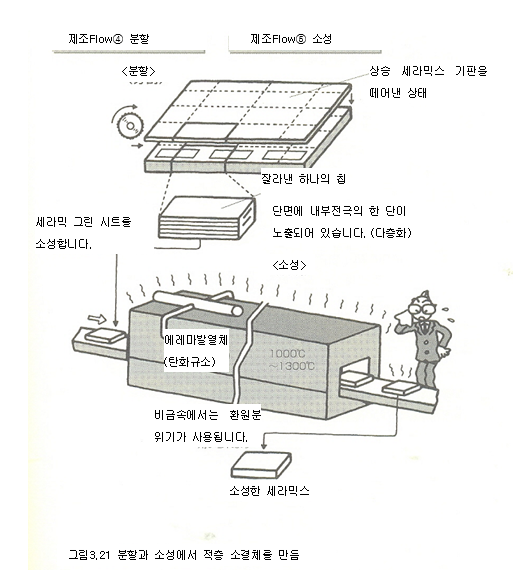

3-7-5 분할 및 소성

가압된 적층 세라믹 그린 시트는 칩 세라믹 콘덴서의 사이즈로 분할되고, 이것을 로에서 소성하는 공정으로 가게 됩니다. 여기에서 겨우 세라믹 그린칩 콘덴서의 모습이 나타나게 됩니다. (그림 3.21)

* 분할: 가압된 적층 세라믹 그린 시트는 Dicing saw(다이스 절단기)로 X축과 Y축 을 절단하고, 칩 사이즈로 분할됩니다. Dicing saw는 일반적으로 미립 다이아몬드를 단 블레이드를 고속회전 하여 절단합니다. 이것이 분할 공정입니다. 이 때, 칩의 측면을 보면, 각 세라믹 그린 시트 층에서 내부전극의 한쪽 끝이 노출된 상태입니다.

* 소성: Dicing saw로 분할한 적층 세라믹 그린 시트의 칩은 건조된 상태입니다. 이 상태의 적층 세라믹 그린 칩을 1000℃~1300℃의 로에서 소성합니다. 이 소성에서, 부드러운 건조 상태의 그린 세라믹은 매우 딱딱한 세라믹 상태가 됩니다. 이 공정에 의해, 내부 전극과 세라믹과 일체화한 적층 소성체가 완성됩니다. 이 때, 균일하고 틀어짐이 없는 칩으로 만드는 것이 중요합니다.

* 미세화로 문제가 되는 팽창계수: 칩 사이즈가 작아짐에 따라서 중요시 되는 점이, 각각의 물체가 가지는 팽창계수의 차이 입니다. 이 팽창계수의 차이에 따라서 온도가 변화하는 경우, 형상이 틀어지거나, 깨지거나, 접촉 불량이 생기거나, 신뢰성 상에서 문제가 생기게 됩니다. 이것을 회피하기 위해서 사용재료는 모두 팽창계수가 비슷한 재료를 사용하거나, 완충재를 삽입하는 대책 및 형상의 연구 등이 필요하게 됩니다. 그 외, 정전문제 및 기전력 등에 대해서도 검토가 필요합니다.

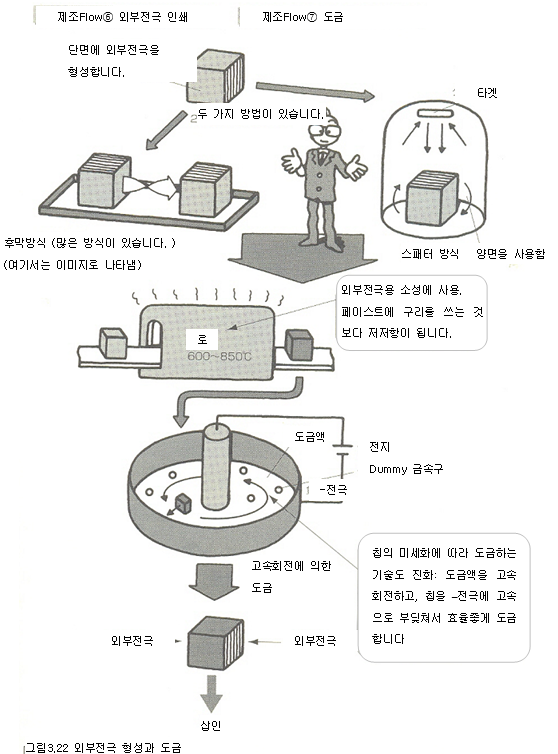

3-7-4 외부전극 형성과 도금

소결이 끝난 적층 세라믹 칩에서는 각 층 마다 내부전극이 노출되어 있습니다. 이 노출된 내부전극을 접속하고 외부전극을 형성하면 이것이 외부단자가 됩니다. 이것을 실시하는 공정이 외부전극 형성과 도금입니다. (그림3.22) 이러한 공정은 먼지를 막기 위해, 크린 룸 내에서 작업이 이루어집니다.

* 외부전극 도포/ 소성: 소성한 적층 소결체에서는 아직 내부전극과 외부전극이 되 는 단자와의 접속이 되어있지 않습니다. 이 때문에, 먼저 칩의 양 끝면에 일반적으로는 比저항이 작은 귀금속인 팔라듐 Pd 및 은/팔라듐 (Ag/Pd) 도전 페이스트를 딥 방식으로 도포합니다. 그 다음, 로에 따라 600℃~850℃로 소성합니다. 이에 의해 내부전극과 내부전극을 접속한 외부전극이 형성됩니다.

* 외부전극 도금: 내부전극이 귀금속인 팔라듐 Pd 및 은/팔라듐 (Ag/Pd)의 경우, 측면에 도체를 입힌 칩 전극에, Leaching을 방지하기 위한 니켈 Ni을, 더욱 납땜성을 높이기 위해서 그 위에 주석 Sn을 도금합니다. 低저항화와 cost 절감면에서, 외부전극에는 구리 Cu가 검토되고 있습니다.

* 전극에 대한 고찰: 칩 외부에 도금한 경우, 온도 변화가 심한 응용분야에서 사용하면, 칩 자체의 팽창계수와 도금의 팽창계수의 차이로 벗겨지는 경우가 발생할 수 있습니다. 이에 대한 대책으로, 칩과 도금 층 중간에 부드러운 도전성 수지를 삽입하고, 팽창계수의 차이를 흡수하는 방법 등을 생각할 수 있습니다. 이러한 대책이 여러 공정에서 요구 되고 있습니다.

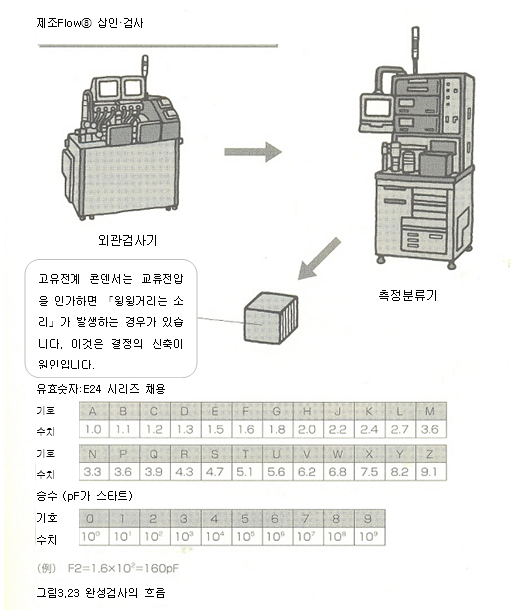

3-7-7 검사

완성한 칩 세라믹 콘덴서는 완성검사를 실시합니다.

완성검사의 측정

칩 세라믹 콘덴서의 완성검사로는, 각종 항목이 측정됩니다. (그림3.23)

* 용량값: 용량값이 지정된 범위에 있는지에 대해서 엄중하게 측정합니다.

* 누전류: 이것은 두 가지가 있습니다. 하나는, 유전체의 절연저항에 의해 흐르는 전류 Id입니다. 또 한가지는 유전체의 분극이 전압변화에 바로 대응하지 못하고, 시간적으로 늦어짐에 따라 감쇄하면서 발생하는 전류 Iav입니다. 이러한 값은 작을수록 좋습니다.

* 유전체 정접(正接): 유전체의 분극이 전압변화에 따라가지 못하기 때문에, 유전체 손실이 발생합니다. 유전체 정접 tanδ

은 손실의 비율을 나타내었습니다. 이것은 인피던스를 등가직열저항성분축과 리액턴스분축에 의해 나타내었을 때의 각도로, 다음과 같이 나타내었습니다. (Q: Quality factor)

tanδ = 등가저항성분 / 리액턴스성분 = ωCR = 1/Q

여기에서 콘덴서에 직류전압을 인가했을 때, 교류전류는 90도 진행되겠지만, 등 가저항성분에 의해 δ만큼 틀어지게 됩니다. 이것이 콘덴서의 에너지 손실로 이어져 발열합니다. 유전체 정접 tanδ은 작을수록 좋습니다. 세라믹 콘덴서에서는 절연체의 저항은 무시하며, tanδ = tanδo 로 간주합니다. (tanδo : 유전체 그 자체의 값)

* CV적: 이것은 콘덴서의 정전용량 C와 정격전압 V와의 곱으로 전하량Q의 크기 입니다.

* 등가직렬저항: 콘덴서가 가지는 인피던스(등가직렬 저항분 ESR과 리액턴스분1/jwC) 안에 있는 등가직렬 저항성분(ESR: Equivalent Series R)을 말합니다. 여기에는, 유전체의 흡수전량 및 전극, 리드선의 저항성분이 모두 포함됩니다. ESR의 값이 크면 전류에 의해 발열이 증가합니다.

* 등가직렬 인덕턴스: 고주파 특성에서 중요한 것이 등가직렬 인덕턴스(ESR: Equivalent Series L)로, 이것은 작을수록 좋습니다.

* 정전용량 변화율: 정전용량 변화율= {(Ct-C20)/C20}*100% t: 주변온도에서의 용량, C20: 20℃에서의 용량

* 정격전압: 이것은 2가지가 있습니다 .하나는 최고사용온도로 연속해서 인가할 수 있는 직류전압과 교류전압의 최대 전압중 높은 전압치를 의미합니다. 또 한가지는 교류에서 실행치의 최대 전압입니다.

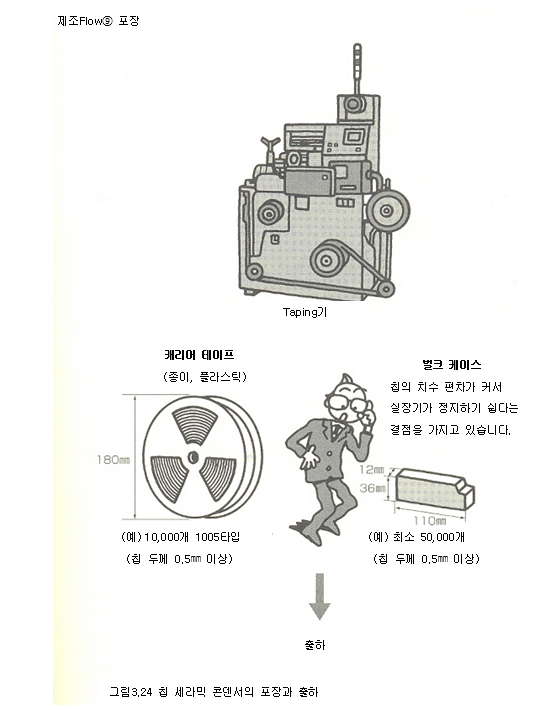

3-7-8 포장/ 출하

칩 세라믹 콘덴서의 검사가 끝나면, 다음은 포장하여 출하합니다. 여기에서는 칩 세라믹 콘덴서의 용량값은 1종류만으로 생각하였습니다. 그러나, 실제로는 매우 많은 용량값이 있습니다. 이에 대응하여, 각종 용량값의 칩 세라믹 콘덴서가 만들어집니다.

포장

칩 세라믹 콘덴서는 매우 작기 때문에, 포장 방법은 연구가 필요합니다. 실제 사용하는 것은 자동 Assembly machine이기 때문에, 직접 이 기계로 사용할 수 있도록 2가지 포장형태가 사용됩니다. (그림3.24)

* 캐리어 테이프: 이것은 하나 하나 완성된 칩 세라믹 콘덴서를 릴 팩키지의 캐리어 테이프에 탑재하는 방법입니다. 이 테이프는 플라스틱 또는 종이 릴에 감겨져 있습니다. 플라스틱 1개의 플라스틱 릴의 직경은 178mm와 330mm가 있습니다. 캐리어 테이프에는 1005 타입(1.0mm×0.5mm×0.5mm)의 칩 세라믹 콘덴서가 10000개 수납, 그 외 벌크품도 있습니다.

* 벌크 케이스: 이것은 벌크 케이스에 탑재하는 방법입니다. 이 실장 방법은 보관장소가 작고, 캐리어 테이프를 사용하지 않기 때문에 자원 절약 등의 이점이 있습니다. 1개의 벌크 케이스의 크기는 110mm×36mm×12mm로, 1005타입(1.0mm×0.5mm×0.5mm)의 칩 세라믹 콘덴서가 최소 50000개 수납됩니다.

출하

이것으로 칩 세라믹 콘덴서는 출하되지만, 그 용량 값의 종류는 매우 다양합니다. 하나의 전자기기에서는 10종류 정도의 용량 값을, 각각 다른 개수만큼 사용합니다. 이에 대해, 출하는 틀림없이 대응해 나가야만 합니다. 또한 신뢰성에 대해서도 시험이 이루어집니다.

'2004-알기쉬운 칩부품의 제조공정' 카테고리의 다른 글

| 알기쉬운 칩부품의 제조공정- 목차 (0) | 2022.08.06 |

|---|---|

| 제 3장 콘덴서 (C)가 만들어지기 까지(1절~4절) (0) | 2021.07.25 |